# Xgig 16-lane Exerciser/Analyzer

## for PCI Express® 6.0

The PCIe® Exerciser/Analyzer generates PCIe 6.0 data streams and responses for in-depth testing and analysis at 64GT/s.

The VIAVI Xgig® PCIe 6.0 Exerciser/Analyzer, the 6P16, brings the next generation of high-speed 64 GT/s test capability to the Xgig PCIe product portfolio. The Exerciser is a valuable tool for debugging difficult protocol communication problems because it provides full, bit-level, repeatable control for generated PCIe 6.0, CXL® and NVMe® data traffic. The Analyzer allows detailed views of traffic between a host and endpoint device, supporting PCIe Flit Mode, Non-Flit Mode, CXL, and NVMe.

The Exerciser generates PCIe compliant traffic and can be configured to emulate the operation of a Root Complex (RC or host system) or an Endpoint (EP) device. Ordered Sets (TSO, TS1, TS2, etc.), and TLP, DLLP, and LTSSM sequences can be defined, transmitted, and even modified in real-time based on user configuration.

The 6P16 Exerciser enables detailed validation and debug of the state machine of a PCle 6.0 controller. It can provide insights for performance tuning of firmware and application software. The 6P16 can be programmed to generate non-compliant PCle sequences to enable testing of boundary and stress conditions that are not normal to correct system operation and would otherwise be very difficult to evaluate.

### **Key Features**

- Generates and responds to PCIe 6.0 64GT/s traffic

- Operates at 64GT/s PAM4, and supports all other PCle data rates of 2.5, 5.0, 8.0, 16, and 32GT/s NRZ

- Supports links of 1, 2, 4, 8 and 16-lanes

- 64 GB total memory (32 GB to capture upstream and 32 GB to capture downstream)

- Dimensions 600 mm x 440 mm x 110 mm

- Power Rating: 100-240 VAC, 50/60 Hz, 15 A, 1500 W

- User can set Exerciser link rates and widths and control transitions to other rates

- Fully integrated Analyzer/Exerciser enables a variety of test conditions

- Analyzer/Exerciser supports new PCle Flit Mode, FEC and TSO Ordered Set

- Exerciser can create unique LTSSM test conditions via user customized branching

- LTSSM state tracker with history log

- Versatile scripting API allows user to define, create and save custom test configurations

- Powerful graphical control interface provides quick status information and fast setup of test cases

- Xgig Analyzer/Exerciser tools operate on a Windows enabled PC

The 6P16 Exerciser works in tight association with the Analyzer function to allow capture and decoding of complex test scenarios. Bidirectional captures can be saved for detailed analysis using VIAVI tools such as Expert $^{\text{TM}}$ .

A scripting API is available so that complex, custom Exerciser test scripts can be created; either as original or modified from pre-defined library scripts.

The VIAVI PCIe 6.0 6P16 Exerciser/Analyzer Solution is a comprehensive solution with Exerciser and Analyzer functionality provided via a multi-function chassis and application-specific Analyzer or Exerciser Interposers.

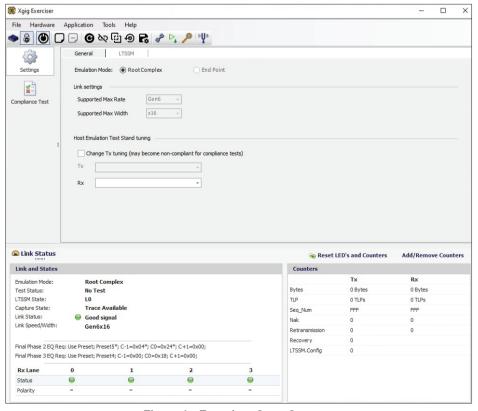

#### **Exerciser User Interface**

The Xgig PCIe Exerciser user interface makes it easy to set up and execute a test. Figure 1 below shows the Exerciser launch screen. The top bar includes the typical Windows<sup>TM</sup> control items. The second bar down has various quick launch buttons for tasks done often.

On the left side are icons for Settings, Compliance Tests, and other features. The **Settings>General tab** is the first that is presented. Information on the test bench configuration is provided including clocking, reset and other basic controls.

From Settings, controls for the extensive Exerciser parameters are accessible. The **LTSSM tab** provides control over link settings and operation.

For example, TX and RX setting can be adjusted from this tab. It also allows setting timeouts and other parameters. The **Settings tab** allows forcing limits on the test data rate and maximum link width.

Below the Settings icon, the **Compliance Test icon** opens a panel for selecting tests to be run.

Below the Compliance Test icon, the **Config Space icon** opens for defining the Exerciser's PCle configuration space parameters.

Always available at the bottom of the Exerciser window is the current test and bench status.

Figure 1 - Exerciser Start Screen

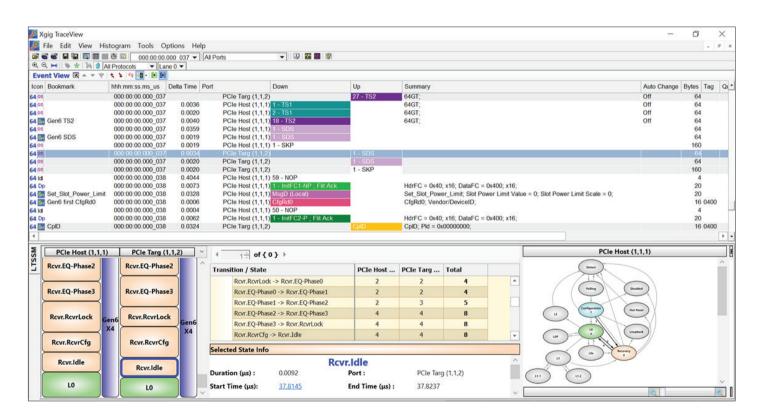

### **Xgig Analyzer User Interface**

The Xgig PCle 6.0 Analyzer/Exerciser user interface makes it easy to set up triggers, filters, trace depth, and start capturing PCle traffic. The 6P16 hardware chassis and complementary Xgig software tools can support PCle 6.0, CXL and NVMe.

The analyzer can be configured to alert the user to protocol errors at every layer of the PCle stack including state and sub-state level errors within the LTSSM Viewer. Further, detection of Flit packing, FEC, and CRC errors enable the user to get an accurate understanding of issues unique to the new PCle 6.0 protocol.

The Xgig PCle 6.0 Analyzer provides the foundation for deep protocol insights provided by the Xgig Expert tools. The transition from PCle 5.0 to PCle 6.0 brought significant changes at the protocol level,

and with it the need for strong analysis tools to fully understand the protocol behavior. The combination of Xgig Analyzer and Expert provides the user incredible utility and flexibility in analyzing and debugging protocol issues.

The 6P16 Analyzer operates to 64GT/s and pairs with the new VIAVI series of function-specific Analyzer Interposers. The new PCle 6.0 Interposers from VIAVI have been architected with a view to preserving signal integrity to limit impact on the link and provide the user a clear view of traffic on the link. The chassis and interposers are backward compatible with all other PCle data rates.

Figure 2 - PCle6 Trace Capture with Xgig Analyzer

# **Test Applications**

The following table lists some of the features available and tests that can be done using the Xgig PCle Exerciser.

| Support for new PCIe Flit Mode                   | Define IO write address space size and offset    |

|--------------------------------------------------|--------------------------------------------------|

| Support for new PCIe FEC                         | Define ROM write address space size and offset   |

| Support for new TS0 Ordered Set                  | Define Cfg read address space size and offset    |

| Support for 64GT/s PCIe 6.0 PAM-4 signaling      | Define Mem64 read address space size and offset  |

| Control clock sources                            | Define Mem32 read address space size and offset  |

| Control and validate reset functions             | Define IO read address space size and offset     |

| Control DUT power                                | Define ROM read address space size and offset    |

| LTSSM supported states: Detect, Quiet,           | Supports Config Space Type O Headers (32b)       |

| Configuration, L0, L1, Recovery                  | Supports Config Space Type 1 Headers (64b)       |

| Set data rate                                    | Inject disparity errors option                   |

| Set link width                                   | Inject symbol errors option                      |

| Edit LTSSM state transitions                     | Inject Sync Bit errors option                    |

| Control link width changes                       | Define ACK/NACK policies                         |

| Control link rate changes                        | Control ACK/NACK DLLP generation/reception       |

| Test transitions: any speed/width to any other   | Control idle generation                          |

| Control link state changes                       | Auto generate TLP sequence numbers               |

| Set TX parameters                                | Auto generate TLP LCRC                           |

| Set RX parameters                                | Auto retransmit TLPs that NACK'd                 |

| Control equalization procedure                   | Validate state timeouts                          |

| Generates TLP 32b memory packets                 | Set replay timeouts                              |

| Generates TLP 64b memory packets                 | Control SKP generation                           |

| Generates TLP IO packets                         | Control over 8b/10b and 128b/130b encoding       |

| Generates TLP configuration packets              |                                                  |

| Generates TLP message packets                    | Control and monitor sideband signals             |

| Execute bad TLP packets                          | Define custom test configurations, save and load |

| Define TS0/TS1/TS2 data                          | Define custom test suites and execution sequence |

| Define Cfg write address space size and offset   | View test description                            |

| Define Mem64 write address space size and offset | View test results                                |

| Define Mem32 write address space size and offset | View LTSSM log                                   |

Ordering Information Data Sheet

| Part Number            | Description                                   |

|------------------------|-----------------------------------------------|

| XGIG6P-PCIE6-X16-PF    | PCIe 6.0 16-Lane Analyzer/Exerciser Platform  |

| XGIG6P-PCIE6-X16-AN    | PCIe 6.0 16-Lane Analyzer License Key         |

| XGIG6P-PCIE6-X16-EX    | PCIe 6.0 16-Lane Exerciser License Key        |

| XGIG6P-PCIE6-X16-PF-H1 | Optional 1-year extended hardware warranty    |

| XGIG6P-PCIE6-X16-PF-M1 | Optional 1-year extended software maintenance |

#### **Accessories**

| Accessories           |                                                      |

|-----------------------|------------------------------------------------------|

| XGIG6P-PCIE6-X16-AIC  | PCIe 6.0 x16 Analyzer Interposer CEM                 |

| XGIG6P-PCIE6-X8-AIC   | PCIe 6.0 x8 Analyzer Interposer CEM                  |

| XGIG6P-PCIE6-X16-EIC  | PCIe 6.0 x16 Exerciser EP Interposer CEM             |

| XGIG6P-PCIE6-X16-TSC  | PCIe 6.0 x16 Host Exerciser Test Stand CEM           |

| XGIG6P-PCIE6-X16-AIEE | PCIe 6.0 x16 Analyzer Back End EDSFF                 |

| XGIG6P-PCIE6-X4-IE1.S | PCIe 6.0 x4 Analyzer/Exerciser Front End EDSFF E1.S  |

| XGIG6P-PCIE-X8-IE1.S  | PCIe 6.0 x8 Analyzer/Exerciser Front End EDSFF E1.S  |

| XGIG6P-PCIE6-AIE1.S   | E1.S DUT Carrier                                     |

| XGIG6P-PCIE6-X4-IE1.L | PCIe 6.0 x4 Analyzer/Exerciser Front End EDSFF E1.L  |

| XGIG6P-PCIE-X8-IE1.L  | PCIe 6.0 x8 Analyzer/Exerciser Front End EDSFF E1.L  |

| XGIG6P-PCIE6-AIE1.L   | E1.L DUT Carrier                                     |

| XGIG6P-PCIE6-X4-IE3   | PCIe 6.0 x4 Analyzer/Exerciser Front End EDSFF E3    |

| XGIG6P-PCIE6-X8-IE3   | PCIe 6.0 x8 Analyzer/Exerciser Front End EDSFF E3    |

| XGIG6P-PCIE-X16-IE3   | PCIe 6.0 x16 Analyzer/Exerciser Front End EDSFF E3   |

| XGIG6P-PCIE6-AIE3     | E3.X DUT Carrier                                     |

| XGIG6P-PCIE-x16-IOCP3 | PCIe 6.0 x16 Analyzer/Exerciser Front End EDSFF OCP3 |

| XGIG6P-PCIE6-AIE0CP3  | OCP3 DUT Carrier                                     |

| XGIG6P-PCIE6-X16-TSED | PCIe 6.0 x16 Host Exerciser Test Stand EDSFF         |

|                       |                                                      |

Accessories configured at time of order.

viavisolutions.com

Contact Us +1844 GO VIAVI | (+1844 468 4284)

To reach the VIAVI office nearest you, visit viavisolutions.com/contact

© 2025 VIAVI Solutions Inc.