Application Note

# Using MDIO in ONT CFP/CFP2 Modules

## **MDIO History**<sup>1</sup>

Management Data Input/Output, or MDIO, is a two-wire serial control bus used to manage physical-layer devices (PHYs) in media access controllers (MACs) inside Gigabit Ethernet equipment which requires accessing and modifying their various registers. MDIO is used for first- and second-generation carrier-frequency pulse modules (CFP and CFP2) (QSFP+ 40 G modules use I<sup>2</sup>C, which is another serial control bus).

MDIO was originally defined in Clause 22 of IEEE RFC802.3 as a single MDIO interface that could access up to 32 registers in 32 different PHY devices. These registers provide status and control information such as link status, speed ability and selection, power down for low-power consumption, duplex mode (full or half), auto-negotiation, fault signaling, and loopback.

MDIO was expanded to meet the needs of faster (10 G+) Ethernet devices as defined in Clause 45 of the 802.3ae specification which extended MDIO capabilities to include:

- Ability to access 65,536 registers in 32 different devices on 32 different ports

- Additional OP-code and ST-code for indirect address register access for 10 GE

- End-to-end fault signaling

- Multiple loopback points

- Low-voltage electrical specification (1.2 V bus)

## Theory of Operation

The MDIO bus has a management data clock (MDC) signal in addition to the MDIO signal. Other associated signals include module address pins A0, A1, and A2 which are used to set the module address.

MDIO uses specific terminology to define the various devices on the bus. The device driving the MDIO bus is identified as the station management entity (STA). The target devices that the MDC manages are known as MDIO manageable devices (MMD).

The STA initiates all communication in MDIO and drives the clock on the MDC which is specified to have a frequency of up to 4 MHz (updated from 2.5 MHz in the CFP MSA). When a CFP or CFP2 is inserted into the appropriate JDSU ONT, it then assumes the STA's role for as long as the CFP/CFP2 is the MMD.

Additional Clause 45 details can be found on the IEEE 802.3 workgroup website. http://www.ieee802.org/3/ba/index.html

<sup>1.</sup> Source: Total Phase, Inc., Knowledge Base - Article 10042: MDIO Background, 2012. <a href="http://www.totalphase.com/support/kb/10042/">http://www.totalphase.com/support/kb/10042/</a>>

## **MDIO and the VIAVI ONT**

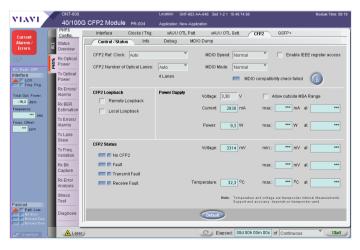

MDIO is required to control and monitor CFP/CFP2 modules and it also enables an ONT to read several important module parameters as shown in Figure 1, including:

- vendor name and ID

- module version and serial number

- module capabilities

- transmitted/received optical power

- module temperature

- module supply voltage

Figure 1. The ONT CFP2 overview screen displays key information provided by the module's MDIO.

Other MDIO registers may let you control and monitor important module elements as shown in Figure 2, such as lasers, CDRs, and receivers. It is possible to use a CFP/ CFP2 without the MDIO (and instead using the control pins); however, it limits both the functionality and capabilities.

Figure 2. The ONT MDIO application lets you control the MDIO bus using two important parameters.

## **MDIO Mode**

The ONT supports these four MDIO operation modes:

- Normal (bus runs at 1.25 MHz and 2 MHz for the CFP and CFP2, respectively) — Normal operation mode supports auto increment read, which is optimized for quick read/write. A checksum at 807F (CFP NVR1 checksum) is validated for correct value.

- 2. Relaxed (bus runs at 1.25 MHz and 2 MHz for the CFP and CFP2, respectively) — In Relaxed operation mode has a longer pause time (190 ns minimum) between address and read/write accesses. Also, auto increment is not used and checksum is ignored. It is also optimized for the most reliable operation.

- 3. External For the CFP, the external mode allows external devices to fully control the MDIO bus within the instrument. The external device can completely control bus speed, timing, and other parameters. For the CFP2, the external MDIO application displays an MDIO control port via a connector on the front of the ONT CFP2 that is fully controlled by the ONT CFP2 MDIO application.

- 4. Disabled No MDIO operation, therefore, the values displayed on the GUI should be considered invalid.

## **MDIO Speed**

The ONT CFP2 module supports three MDIO bus speeds:

- 1. Normal (bus runs at 2 MHz) Normal is the default speed; however, the ONT CFP module runs the MDIO at a slower speed of 1.25 MHz.

- 2. Fast (bus runs at 4 MHz) Fast is the fastest speed defined in the CFP Multi-Source Agreement (MSA).

- 3.Slow (bus runs at 500 kHz) Slow is a very slow speed which helps to support debugging.

# MDIO Pinout on CFP and CFP2 Modules

#### **CFP Module**

Figure 3 shows the pinout for the CFP module. The table that follows provides pinout details.

Figure 3. ONT CFP module pinout

### CFP2 Module

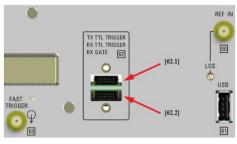

Figure 4 shows the pinout for the CFP2 module. The tables that follow list the pin assignments.

Figure 4. ONT CFP2 module pinout

Note: RJ45 pinning and electrical levels are **not** compatible with Ethernet. Avoid connecting the MDIO port to an Ethernet port.

|               |     |        |                 |          |          | Pull-Up/        |                                                         |

|---------------|-----|--------|-----------------|----------|----------|-----------------|---------------------------------------------------------|

| Signal        | Pin | IN/OUT | Level           | "H"      | "L"      | Down            | Additional Information                                  |

| MDIO          | 3   | IN/OUT | 1.2 V<br>LVCMOS | _        | _        | Up<br>(470 Ohm) | Management data                                         |

| MDC           | 1   | IN/OUT | 1.2 V<br>LVCMOS | _        | _        | Up<br>(470 Ohm) | Management clock                                        |

| MOD_RSTn      | 4   | IN     | 3.3 V<br>LVCMOS | Enable   | Reset    | Up<br>(10k Ohm) | Module reset                                            |

| MOD_<br>LOPWR | 8   | IN     | 3.3 V<br>LVCMOS | Deselect | Enable   | Up<br>(10k Ohm) | Module low-power mode                                   |

| MOD_ABS       | 7   | OUT    | 3.3 V<br>LVCMOS | Absent   | Present  | Open drain      | Module absent<br>Use external pull up 4.7 to<br>10k Ohm |

| GLB_ALRM      | 5   | OUT    | 3.3 V<br>LVCMOS | Alarm    | No alarm | N/A             | Global alarm                                            |

| GND           | 2   | N/A    | N/A             | N/A      | N/A      | N/A             | Ground                                                  |

| GND           | 6   | N/A    | N/A             | N/A      | N/A      | N/A             | Ground                                                  |

#### Pinout

## Pin Assignment List of ERNI SMC Connector (Top)

| Pin 11   | Pin 9      | Pin 7           | Pin 5     | Pin 3     | Pin 1     |

|----------|------------|-----------------|-----------|-----------|-----------|

| not used | GND        | External Trigge | GLB_ALRMn | PRG_ALRM3 | PRG_ALRM1 |

| GND      | RX Gate in | not used        | MOD_ABS   | RX_LOS    | PRG_ALRM2 |

| Pin 12   | Pin 10     | Pin 8           | Pin 6     | Pin 4     | Pin 2     |

| Signal        | Pin | IN/OUT | Level           | "H"            | "L"      | Pull-Up/<br>Down | Additional Information  |

|---------------|-----|--------|-----------------|----------------|----------|------------------|-------------------------|

| PRG_ALRM 1    | 1   | IN     | 3.3 V<br>LVCMOS | Alarm          | No alarm | Up<br>(10k Ohm)  | Programmable alarm 1    |

| PRG_ALRM<br>2 | 2   | IN     | 3.3 V<br>LVCMOS | Alarm          | No alarm | Up<br>(10k Ohm)  | Programmable alarm 2    |

| PRG_ALRM<br>3 | 3   | IN     | 3.3 V<br>LVCMOS | Alarm          | No alarm | Up<br>(10k Ohm)  | Programmable alarm 3    |

| RX_LOS        | 4   | IN     | 3.3 V<br>LVCMOS | Loss of signal | OK       | Up<br>(10k Ohm)  | Loss of receiver signal |

| GLB_ALRMn     | 5   | OUT    | 3.3 V<br>LVCMOS | Alarm          | No alarm | Up<br>(10k Ohm)  | Global alarm            |

| MOD_ABS       | 6   | IN     | 3.3 V<br>LVCMOS | Absent         | Present  | Up<br>(10k Ohm)  | Module absent           |

| GND           | 9   | N/A    | N/A             | N/A            | N/A      | N/A              | Ground                  |

| GND           | 12  | N/A    | N/A             | N/A            | N/A      | N/A              | Ground                  |

#### Pin Assignment List of ERNI SMC Connector (Bottom)

| Pin 2     | Pin 4     | Pin 6     | Pin 8    | Pin 10 | Pin 12 |

|-----------|-----------|-----------|----------|--------|--------|

| PRG_CNTL2 | TX_DIS    | MOD_RSTn  | not used | MDC    | GND    |

| PRG_CNTL1 | PRG_CNTL3 | MOD_LOPWR | not used | GND    | MDIO   |

| Pin 1     | Pin 3     | Pin 5     | Pin 7    | Pin 9  | Pin 11 |

| Signal         | Pin | IN/OUT | Level           | "H"      | "L"    | Pull-Up/<br>Down | Additional Information |

|----------------|-----|--------|-----------------|----------|--------|------------------|------------------------|

| PRG_CNTL 1     | 1   | OUT    | 3.3 V<br>LVCMOS | _        | _      | N/A              | Programmable control 1 |

| PRG_ CNTL<br>2 | 2   | OUT    | 3.3 V<br>LVCMOS | _        | _      | N/A              | Programmable control 2 |

| PRG_ CNTL<br>3 | 3   | OUT    | 3.3 V<br>LVCMOS | —        | —      | N/A              | Programmable control 3 |

| TX_DIS         | 4   | OUT    | 3.3 V<br>LVCMOS | Disable  | Enable | N/A              | Transmitter disable    |

| MOD_<br>LOPWR  | 5   | OUT    | 3.3 V<br>LVCMOS | Deselect | Enable | _                | Module low-power mode  |

| MOD_RSTn       | 6   | OUT    | 3.3 V<br>LVCMOS | Enable   | Reset  | _                | Module reset           |

| GND            | 9   | N/A    | N/A             | N/A      | N/A    | N/A              | Ground                 |

| MDC            | 10  | IN/OUT | 1.2 V<br>LVCMOS | _        | _      | Up<br>(470 Ohm)  | Management clock       |

| MDIO           | 11  | IN/OUT | 1.2 V<br>LVCMOS | _        | _      | Up<br>(470 Ohm)  | Management data        |

| GND            | 12  | N/A    | N/A             | N/A      | N/A    | N/A              | Ground                 |

The MDIO address pins are hard wired in the ONT, where A0=1, A1=0, and A2=0.

## Conclusion

The ONT MDIO compatibility check is not simply a pass/fail test. Rather, it provides additional information to help support R&D to develop and debug CFP and CFP2 modules. The robust ONT MDIO support works under most conditions and is not intended for use as an MDIO compliance test.

Check the following if the ONT indicates an MDIO compatibility check failure:

- Checksum at 807F (CFP NVR1 checksum)

- Module support for auto increment read

- Address 0x8000 module identifier

The module can operate via MDIO relaxed mode without serious issues if required (ignoring checksum and without auto increment).

Remember that the compatibility check provides useful information; however, avoid relying on it as simply a definitive module pass/fail test.

Contact Us +1 844 GO VIAVI (+1 844 468 4284)

To reach the VIAVI office nearest you, visit viavisolutions.com/contact

© 2021 VIAVI Solutions Inc. Product specifications and descriptions in this document are subject to change without notice. Patented as described at viavisolutions.com/patents mdio-an-opt-tm-ae 30175755 900 0813