PCIe 5.0

Le plus haut niveau de performance, de rapidité et de robustesse en matière de PCI Express

Produits

-

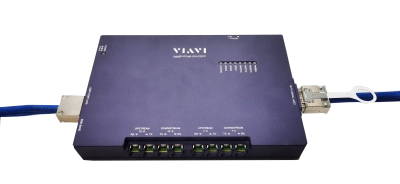

Xgig 5P16 Analyzer / Exerciser / Jammer Platform for PCI Express 5.0

Combines A/E/J functionality on the same platform with support for the latest PCIe, NVMe and CXL specifications, and...

-

Xgig 5P8 Analyzer / Exerciser / Jammer Platform for PCI Express 5.0

Provides full-speed 32Gbps data capture, enabling detailed functional and performance analysis of PCIe protocol...

-

Xgig Exerciser Host Test Stand Interposer Module for PCI Express 5.0

The PCIe Exerciser Host Test Stand provides connectivity and power to a PCIe adapter card endpoint for testing and...

-

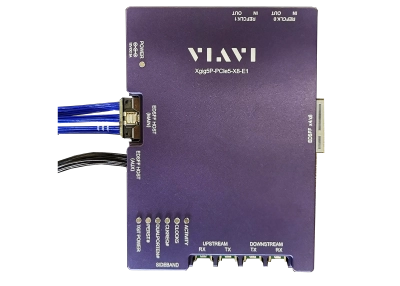

Xgig E1 EDSFF 8-Lane Interposer for PCI Express 5.0

The Xgig® 5P-PCIe5-X8-E1 Interposer is optimized for developing, debugging and performance-tuning NVMe SSD operation...

-

Xgig E3 EDSFF 16-Lane Interposer for PCI Express 5.0

The Xgig5P-PCIe5-X16-E3 Interposer is optimized for developing, debugging and performance-tuning NVMe SSD operation...

-

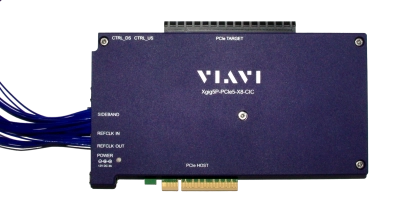

Xgig CEM 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

Xgig CEM 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

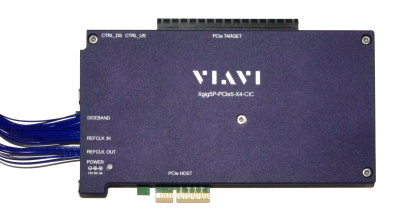

Xgig CEM 4-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 4-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

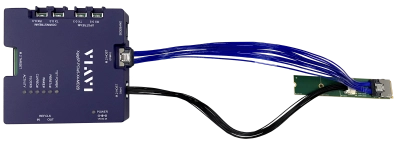

Xgig M.2 4-lane Interposer Module for PCI Express 5.0

The Xgig M.2, 4-lane Interposer for PCI Express® 5.0 is an Active Interposer with a design optimized for M.2 SSD...

-

Xgig U.2-Server, 4-lane Interposer Module for PCI Express 5.0

The Xgig® U.2-Server Interposer is optimized for development, debugging and tuning of NVMe SSD operation in high-...

-

Xgig U.3-Server, 4-lane Interposer Module for PCI Express 5.0

The Xgig® U.3-Server Interposer is optimized for development, debugging and tuning of NVMe SSD operation in high-...

-

Xgig Slimline 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane Slimline Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

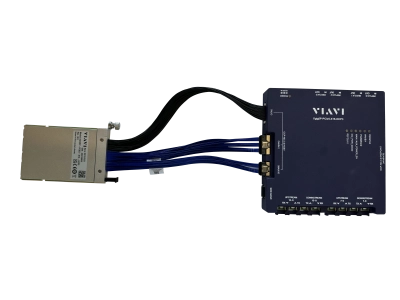

Xgig CDFP 16-lane Interposer for PCI Express 5.0

This PCIe 5.0 16-lane CDFP/CopprLink™ Interposer provides a tap of PCIe data signals between two externally cable-...

-

Xgig OCP3 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane OCP3 Interposer provides a tap of host-system PCIe signals to OCP NIC 3.0 devices for input...

-

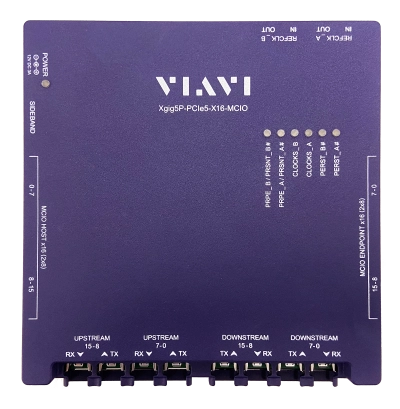

Xgig MCIO 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane MCIO/CopprLink™ Interposer enables protocol analysis of communication between a 16-lane MCIO/...

-

Xgig Flying Lead, 4-Lane Probe for PCI Express 5.0

Provides the data signal connection between a device under test and the VIAVI Protocol Analyzer chassis

-

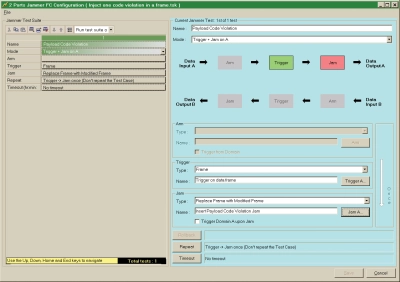

Xgig Jammer for PCI Express 5.0

The Xgig® Jammer manipulates live network traffic to simulate errors in real time, enabling users to verify the...

-

Xgig Exerciser for PCI Express 5.0

The PCIe Exerciser generates PCIe data streams and responses for compliance testing and analysis PCIe 5.0 protocol...

-

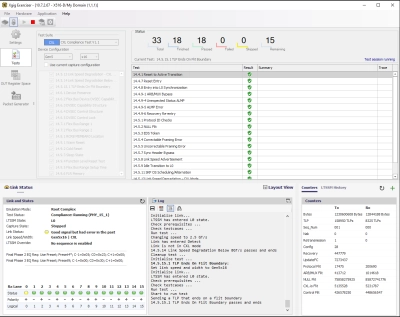

Xgig Exerciser for CXL v1.1/v2.0

Approved for CXL Gold Suite compliance testing, the CXL Exerciser generates CXL data streams and responses for...

-

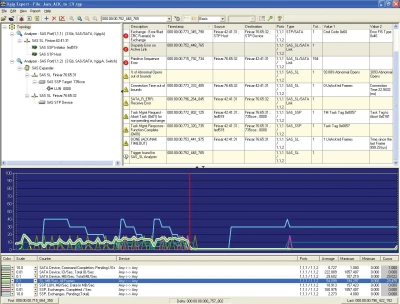

Xgig Expert

Expert software comes standard with all Xgig Analyzers to provide a unique and robust set of debugging and analysis...

-

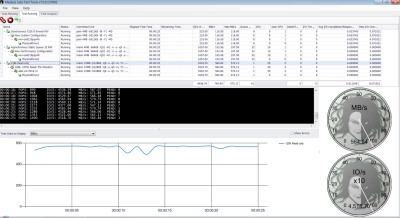

Medusa Labs Test Tools Suite

Medusa Labs Test Tools Suite is the leading application-based data testing and signal integrity testing tool...

La plateforme VIAVI Xgig PCIe5 prend en charge les fonctionnalités d’analyseur, de brouilleur et d’exerciseur, ainsi que des capacités de bifurcation de port d’analyseur et d’utilisation simultanée par plusieurs utilisateurs sur un châssis 5P16 unique. Cette conception plurifonctionnelle contribue à réduire la dépendance envers plusieurs appareils monofonctionnels, ce qui permet une baisse des coûts d’acquisition et de possession. Ces fonctionnalités favorisent une productivité accrue de chaque système pour des valeurs de coût par test/coût par utilisateur inférieures, ainsi qu’un débogage plus rapide permettant une mise sur le marché accélérée.

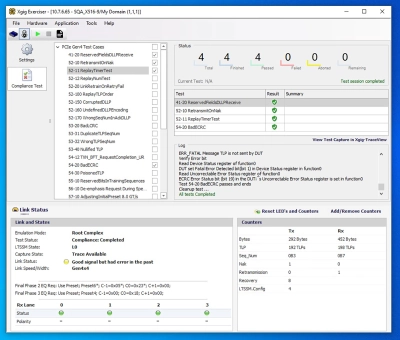

Le Xgig Exerciser est agréé par le Peripheral Component Interconnect Special Interest Group (PCI-SIG) pour une utilisation dans le cadre des tests de certification de la conformité des protocoles PCI Express (PCIe) 4.0 effectués dans les ateliers de vérification de la conformité du PCI-SIG. Le PCIe 4.0 correspond au plus haut niveau de certification de la conformité actuellement proposé par le PCI-SIG.

Qu’est-ce que le PCIe 5.0 ?

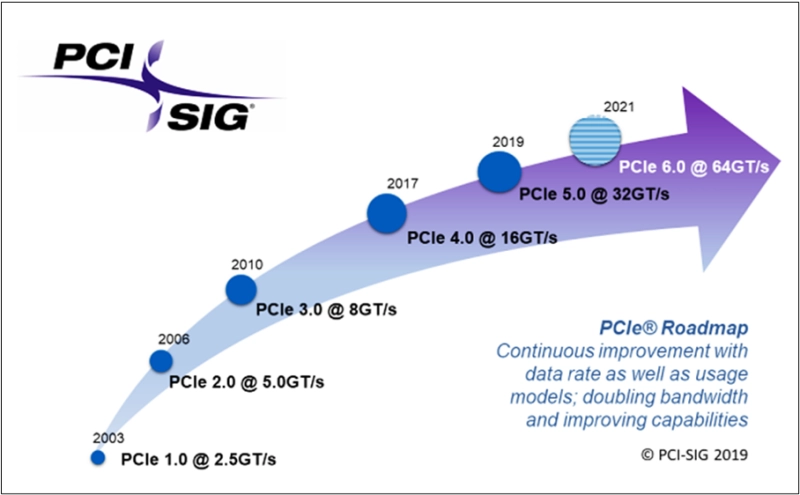

PCI Express 5.0 désigne la cinquième génération de la norme d’interconnexion expresse de composants périphériques. PCIe gen-5, PCIe5 et PCIe 5.0 sont d’autres dénominations couramment employées. Présentée pour la première fois en 2003, la technologie PCIe est devenue l’interface standard pour la connexion de composants haut débit au CPU via un bus d’accès point à point. Si un délai de sept ans sépare l’apparition du PCIe 3.0 de celle du PCIe 4.0, le développement et le lancement des spécifications du PCI Express 5.0 ont suivi de peu ceux du PCIe 4.0 en offrant néanmoins deux fois plus de bande passante. Le consortium PCI-SIG a lancé la norme PCIe 5.0 finale.

Du fait de l’importante augmentation des volumes de données, les normes et pratiques de test sont remises en cause par chaque nouvelle version du PCIe, et le PCIe 5.0 ne fait pas exception à la règle. Par exemple, l’ensemble ordonné de sortie de veille électrique (Electrical Idle Exit Ordered Set, EIEOS) et les fonctionnalités de cadencement révisés ont eu un impact sur les pratiques de test au niveau de l’équipement et du système.

Des protocoles alternatifs exigent également un support complet des tests, car cette polyvalence améliorée permet désormais à d’autres protocoles de tirer parti de la pile de couches physiques PCIe éprouvée.

- Compute Express Link (CXL) est un protocole d’interconnexion supportant la cohérence de cache largement accepté destiné aux processeurs, extensions de mémoire et accélérateurs.

- NVM Express® (NVMe®) définit la façon dont le logiciel hôte communique avec la mémoire rémanente sur de nombreux transports, tels que PCI Express® (PCIe®), RDMA, TCP et autres. Il s’agit de la norme du marché pour les disques durs électroniques (SSD) de tous facteurs de forme (U.2, M.2, AIC, EDSFF).

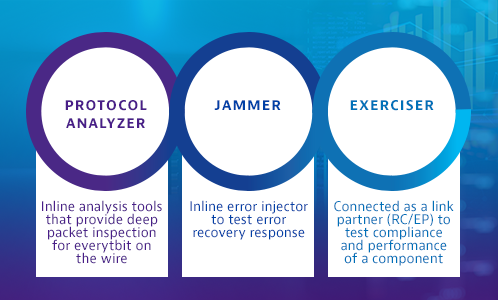

Xgig Analyzers

Les analyseurs de protocoles entièrement compatibles avec le trafic descendant et capables de prendre en charge l’exploitation de liaisons de données de 32 GT/s, comme le Xgig Analyzer de VIAVI, sont extrêmement utiles pour les procédures de test et de débogage du PCIe 5.0. Une segmentation et une capacité de mémoire et de stockage supérieures pour la capture des trafics ascendant et descendant à volume élevé permettent l’enregistrement de longues séquences et le filtrage de paquets spécifiques pour des analyses de protocole fiables. Voir tous les analyseurs de protocoles.

Xgig Exerciser

Le VIAVI Solutions Xgig® Exerciser pour PCIe5 offre une capacité de test de conformité clé en main pour le portefeuille de produits Xgig PCIe.

- Cet outil s’avère utile pour déboguer les problèmes complexes de communication des protocoles, car il offre un contrôle complet, reproductible au niveau du bit, sur le trafic de données PCIe.

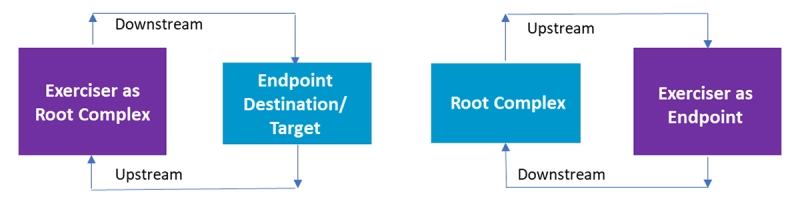

- Il remplace le distributeur de liaison de communication et fournit un contrôle complet sur les tests de complexe pivot ou de point d’extrémité, comme illustré dans le diagramme.

- Il convient parfaitement à l’analyse et au débogage au niveau du composant.

Les Exercisers proposent deux modes d’exploitation. Le mode Hôte, ou Complexe pivot (à gauche), sert à tester les points d’extrémité.

Le mode Point d’extrémité (à droite) sert à tester les systèmes hôtes, les ports de commutation et les CPU.

Le Xgig Exerciser est agréé par le Peripheral Component Interconnect Special Interest Group (PCI-SIG) pour une utilisation dans le cadre des tests de certification de la conformité des protocoles PCI Express (PCIe) 4.0 effectués dans les ateliers de vérification de la conformité du PCI-SIG.Le PCIe 4.0 correspond au plus haut niveau de certification de la conformité actuellement proposé par le PCI-SIG. Voir tous les Exercisers.

Xgig Jammer

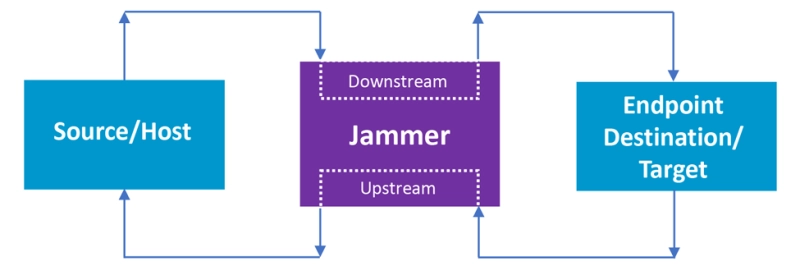

Les Jammers (brouilleurs) agissent en ligne entre le CPU et les points d’extrémité. Ils insèrent des erreurs dans la communication entre les appareils réels du système. Voir tous les Jammers.

- Ils conviennent particulièrement aux tests du système et à l’analyse pour récupération sur erreur.

- La simulation d’un trafic réseau en temps réel constitue un test de mise à l’épreuve important pour le matériel de PCIe.

- Cette simulation permet de s’assurer que les appareils fonctionneront exactement comme ils le doivent en conditions réelles.

- C’est un aspect essentiel pour les produits d’importance critique.

Interposeurs

Les interposeurs permettent de capturer la communication entre un système hôte et un dispositif à l’essai (Device Under Test, DUT). VIAVI propose une gamme complète d’interposeurs PCIe populaires, parmi lesquels :

- Host Test Stand

- CEM

- EDSFF, E1, E3

- U.2, U.3

- U.2 CEM

- M.2

- SFF-8674

- Flying-Lead

- Oculink Slimline

Suite d’outils Xgig

La plateforme Xgig PCIe5 est compatible avec la suite d’outils Xgig qui inclut les produits suivants :

- Xgig Expert™ est une interface conviviale qui facilite l’interprétation, l’analyse des performances et le dépannage rapides des données.

- Xgig Serialytics™ s’appuie sur Xgig Expert pour révéler les comportements et événements cachés dans une trace. Il améliore le débogage contextuel et fournit des analyses intelligentes des protocoles série.

- Xgig Trace Control est l’interface utilisateur de configuration du système dont l’opérateur se sert pour configurer le système en vue des tests.

- Medusa Labs Test Tools Suite (MLTT) est un outil de tests d’intégrité du signal et des données basé sur application permettant aux développeurs d’identifier, de localiser et de corriger les erreurs grâce à des tests de contrainte.

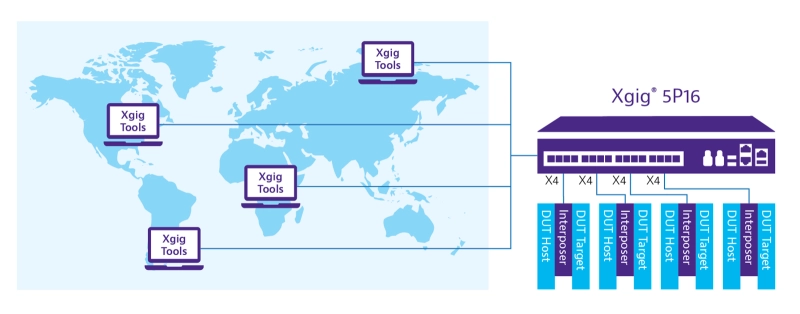

Généralement, dans le cadre de l’analyse de protocole PCI Express®, un utilisateur effectue un test unique sur un équipement monofonctionnel dédié. Désormais, de nombreux utilisateurs peuvent se connecter simultanément au VIAVI Xgig® 5P16 ou 5P8 Analyzer afin d’effectuer des tests indépendants simultanés.

Flexibilité de type multi-utilisateurs simultanés (SMU) rendue possible par la bifurcation

Les utilisateurs n’ont plus besoin de se trouver physiquement au même endroit que l’analyseur. Ils peuvent ouvrir une session à distance, depuis n’importe où dans le monde, s’ils ont accès à un réseau. Le graphique ci-dessous présente un exemple d’analyseur à 16 voies bifurquées en quatre liaisons indépendantes pour permettre à de multiples utilisateurs d’effectuer simultanément des tests distincts.

La bifurcation divise un port normalement affecté à une liaison en deux liaisons ou plus. Comme le montre le graphique ci-dessous, un VIAVI Xgig 5P8 peut être bifurqué en deux liaisons de 4 voies chacune, et un 5P16 en deux liaisons de 8 voies chacune ou en quatre liaisons de 4 voies chacune.

Le châssis Xgig 5P16 prend également en charge les fonctions d’analyseur, d’exerciseur et de brouilleur.

Le système Xgig 5P16, notre produit phare, prend en charge des fonctionnalités complètes d’analyseur, d’exerciseur et de brouilleur sur le même châssis. Une plateforme de ce type, flexible et définie par logiciel, simplifie la gestion de l’équipement. Les mises à niveau logicielles sont mises à disposition plus rapidement et plus économiquement qu’avec des modules matériels. Leur installation peut s’effectuer à tout moment, ce qui permet aux gestionnaires de conserver leurs budgets jusqu’à ce que la mise à niveau soit nécessaire.

La productivité accrue des appareils réduit le délai de commercialisation et diminue globalement le coût total de possession.

Les Xgig Analyzers plurifonctionnels permettent des économies opérationnelles difficilement égalées par les appareils monofonctionnels. Les utilisateurs peuvent ainsi rationaliser les processus de configuration et de débogage, de sorte que les produits et les composants soient testés et commercialisés plus rapidement.

Approuvé pour les tests de certification du PCI-SIG

Le Xgig Exerciser est agréé par le Peripheral Component Interconnect Special Interest Group (PCI-SIG) pour une utilisation dans le cadre des tests de certification de la conformité des protocoles PCI Express (PCIe) 4.0 effectués dans les ateliers de vérification de la conformité du PCI-SIG. Le PCIe 4.0 correspond au plus haut niveau de certification de la conformité actuellement proposé par le PCI-SIG. VIAVI collabore activement avec le PCI-SIG à l’activation des tests de conformité PCIe5.

Le lancement final de la norme PCI Express 5.0 en 2019 a marqué l’aboutissement d’un cycle de développement accéléré de 18 mois jugé nécessaire pour faire face à l’évolution de la demande en matière de performance des applications à traitement de données intensif.

Tout comme les précédentes générations, le PCIe 5.0 conserve sa compatibilité avec les versions antérieures, même si la version (le débit) la plus faible entre le port PCIe et la carte de connexion reste le facteur déclencheur. En plus de l’augmentation de la bande passante, les spécifications du PCIe 5.0 incluent des progrès électriques permettant d’améliorer l’intégrité du signal et les mises à jour mécaniques pour une meilleure performance des connecteurs.

Comme ce fut le cas pour chaque version du PCIe, la coexistence entre le PCIe Express 5.0 et les versions précédentes, rendue possible par la compatibilité à rebours intrinsèque de l’interface PCIe, permet aux applications à haute performance les plus exigeantes, telles que le cloud computing et l’intelligence artificielle (IA), de bénéficier du taux de transfert le plus élevé actuellement disponible alors que les technologies de générations précédentes demeurent utilisables pour les applications moins exigeantes.

La date de lancement du PCIe 5.0 en 2019 n’a constitué que l’une des nombreuses étapes vers sa mise en œuvre. Les tests préliminaires de conformité et d’interopérabilité doivent également être passés avec succès. Ces jalons additionnels pourraient fortement retarder les premières offres commerciales de produits PCIe 5.0 certifiés.

Étant donné que la norme PCIe est intégrée à presque tous les types de systèmes informatiques en usage actuellement, de nombreuses sociétés parmi les plus importantes du monde dans les secteurs de l’électronique, de l’informatique, du stockage de données et du e-commerce œuvrent à la symbiose entre l’infrastructure client et celle de la chaîne d’approvisionnement pour PCI Express 5.0. Cela inclut les fournisseurs d’éléments de propriété intellectuelle (PI) d’activation du PCIe Gen 5, les fabricants de commutateurs et de resynchroniseurs , ainsi que les fournisseurs de cartes mères, de dispositifs de stockage et de contrôleurs graphiques pour PCIe 5.0. Ces éléments de construction essentiels alimentent les systèmes et équipements informatiques avancés pour les datacenters et d’autres déploiements de réseaux fondamentaux.

Segments de marché pour l’adoption anticipée du PCIe 5.0

Toutes les entreprises et tous les segments de marché n’adopteront pas la technologie PCI Express Gen 5 de manière simultanée. Les marchés des biens de propriété intellectuelle exigent des capacités de validation anticipées pour garantir la fonctionnalité dans des formats FPGA ou silicone. Les segments des processeurs, d’Ethernet et de certains accélérateurs sélectionnés seront aux aussi fortement impliqués dans un lancement anticipé du PCIe 5.0. Les serveurs de datacenter et les infrastructures informatiques haute performance (HPC), qui répondent déjà difficilement aux exigences exponentielles en termes de bande passante et de latence, absorberont rapidement les avantages inhérents à la technologie PCIe Gen 5 dès qu’elle sera disponible.

Utilisateurs de l’analyse de protocoles PCIe 5.0

Des cycles de validation et de débogages plus rapides sont essentiels pour accélérer le délai de mise sur le marché. Il en résulte une demande accrue d’outils d’analyse de protocoles PCIe Gen 5 avancée de la part des équipes d’intégration de systèmes chargées de la vérification et de la validation, mais aussi des équipes de débogage responsables de la qualification des composants et de la résolution des problèmes d’interopérabilité. Les équipes spécialisées dans l’affinage de la performance des appareils, des moteurs et des logiciels applicatifs trouvent elles aussi un avantage certain dans la fonctionnalité d’analyse de protocoles PCIe 5.0 avancée.

La convention de doublement du débit à chaque nouvelle version de la norme PCIe s’applique une fois de plus avec le lancement du PCIe 5.0. Avec la même méthode d’encodage 128b/130b standard utilisée depuis la version PCIe 3.0, le PCIe 5.0 fournira un débit de 64 Go/s dans chaque direction. Et puisque la technologie PCIe permet un flux de données bidirectionnel en full-duplex, le débit total pour les deux directions combinées monte à 128 Go/s.

Avant le PCIe 3.0, la norme d’encodage était 8b/10b, ce qui signifie que huit bits de données étaient encodés et transmis sous forme de nombre à 10 bits. Il en découlait un facteur de saturation de la performance de 20 %, et ainsi, un taux de transfert de bits brut de 2,5 GT/s était ramené à une bande passante nette de seulement 2,0 Gbit/s. Avec la convention d’encodage du PCIe 5.0, ce facteur de saturation est de 1,5 % et l’efficacité s’en trouve accrue.

| Version du PCIe | Année de Jahr | Taux de transfert | Débit/voie | Débit x 16 |

|---|---|---|---|---|

| 1,0 | 2003 | 2,5 GT/s | 250 Mo/s | 4,0 Go/s |

| 2.0 | 2007 | 5.0 GT/s | 500 Mo/s | 8.0 Go/s |

| 3.0 | 2010 | 8,0 GT/s | 1,0 Go/s | 16,0 Go/s |

| 4.0 | 2017 | 16,0 GT/s | 2,0 Go/s | 32,0 Go/s |

| 5.0 | 2019 | 32,0 GT/s | 4,0 Go/s | 64,0 Go/s |

L’incroyable vitesse du PCIe 5.0 permet à l’équivalent du contenu type d’un disque Blu-ray d’être transféré vers une mémoire non volatile (NVM) sur une carte mère PCI 5.0 en moins d’une seconde. Et même si ce débit exceptionnel peut sembler être un luxe superflu, il est indispensable pour améliorer l’architecture réseau dans d’autres domaines. Par exemple, l’Ethernet 400G exige une bande passante de 50 Go/s dans chaque direction pour communiquer avec un processeur à capacité maximale.

Au-delà d’Ethernet, ce cycle d’amélioration continue est induit par l’arrivée de systèmes en temps réel dont les exigences de performance rendent la latence essentielle, comme c’est le cas pour conduite autonome, les applications de défense exigeant une réponse instantanée et les applications de sécurité financière critiques pour lesquelles les tentatives de piratage doivent être immédiatement déjouées. Les utilisateurs individuels de systèmes à cartes graphiques multiples ou premium retirent aussi des avantages concrets des améliorations du PCIe 5.0 en termes de débit et de bande passante.

Le PCI Express 5.0 peut être considéré comme une évolution naturelle de la norme PCIe rétrocompatible, avec aucun changement de lien inhérent ni de couche transactionnelle inclus dans cette version. La spécification 5.0 continue à bénéficier d’un contrôle adapté du flux et des identifiants et crédits étendus établis avec le PCIe 4.0.

Un nouveau connecteur CEM conçu pour les cartes d’extension a également été ajouté. Les améliorations des fonctions d’intégrité du signal et de conception des connecteurs ont amélioré la performance et la fiabilité générales. Les améliorations de la couche physique incluent aussi une mise à jour des ensembles ordonnés EIEOS et SKP, et des séquences d’égalisation.

La spécification du PCI Express 5.0 est généralement vantée par les fabricants d’équipement et les acteurs du secteur. Plus particulièrement, les améliorations apportées pour perfectionner la capacité de test, accélérer la formation sur la liaison et fournir un support pour le protocole alternatif sont reconnues comme des caractéristiques exceptionnelles du PCIe 5.0. Le consensus du secteur, ainsi que l’ensemble relativement minime des prérequis de mise en œuvre nécessaires à la transition du PCIe 4.0 vers le PCIe 5.0, sont à l’origine du développement agressif des équipements et des cibles de commercialisation.

Les avancées et les changements de spécification qui accompagnent le lancement du PCIe 5.0 ont encore amplifié le nombre des défis architecturaux propres au PCIe, ce qui complique les activités de test et de développement. Cela inclut la nécessité de diviser par deux la gigue de l’émetteur (Tx) et par trois la gigue d’horloge de référence.

La perte de signal reste un défi architectural persistant avec le PCIe 5.0. Les éléments matériels de base des resynchroniseurs, des réachemineurs et autres cartes de circuits imprimés font partie des options coûts-bénéfices disponibles auprès des concepteurs d’équipements qui souhaitent limiter ces problèmes. Le recours à un resynchroniseur permet de retransmettre le signal alors qu’un réachemineur peut servir à l’amplifier. Dans un cas comme dans l’autre, la portée physique du lien s’en trouvera améliorée.

La spécification du PCI Express 5.0 définit un budget de perte de canaux de 36 db, ce qui est supérieur d’environ 28 % seulement au seuil du PCIe 4.0. L’affaiblissement inhérent à la technologie PCIe est toujours présent dans la version PCIe 5.0. Les niveaux de perte enregistrés avec une construction utilisant des cartes de circuits imprimés FR4 ne sont donc plus viables et des éléments matériels alternatifs tels que le MEGTRON, qui coûtent jusqu’à 2,5 fois plus cher que le FR4, sont devenus obligatoires. De nouvelles conceptions de circuits d’égalisation pour l’émetteur (TX) et le récepteur (RX) sont également rendues indispensables par les besoins du PCI Express 5.0 en matière de canaux, et des marges de voie au niveau du récepteur sont désormais nécessaires autant pour la tension que pour la synchronisation.

Lors du passage du PCIe 4.0 au PCI Express 5.0, le doublement du débit, la rétrocompatibilité et l’accélération du cycle de lancement constituaient les trois piliers essentiels sur lesquels s’était construite la stratégie de mise en œuvre.

Les nouvelles fonctionnalités permettant ou favorisant l’augmentation de la vitesse primaient sur les changements recommandés ou demandés. Par exemple, des changements d’EIEOS et de définition de débit de données étaient nécessaires pour permettre une augmentation de la vitesse, mais des éléments fondamentaux de la norme PCIe, comme la méthode d’encodage et le taux d’erreur binaire (BER) cible, sont restés les mêmes. Les schémas de signalisation et de brouillage sont aussi restés les mêmes que pour le PCIe Gen 4 et les méthodes de tests d’émetteur (Tx) et de récepteur (Rx) ont été utilisées lorsque cela était possible afin de minimiser l’impact de la mise en œuvre.

Malgré l’importance attachée au délai de mise sur le marché et à la compatibilité, d’autres changements conceptuels importants entre les versions PCIe 4.0 et 5.0 ont inévitablement affecté le couplage d’équipements et les pratiques de test. Cela a notamment concerné la récupération des données d’horloge (Clock Data Recovery, CDR) avec une réponse de deuxième ordre et un connecteur CEM uniquement compatible avec un encombrement de circuit imprimé PCBA à montage en surface, bien qu’il demeure rétrocompatible avec les versions antérieures au niveau de l’interface de la carte d’extension. PCI Express 5.0 prend aussi en charge des protocoles alternatifs via des séquences TS1/TS2 modifiées.

La cohérence entre les normes PCIe 4.0 et PCIe 5.0 était d’autant plus nécessaire que le délai de lancement de la norme 4.0 avait été exceptionnellement long, alors que le paysage des réseaux et la demande en bande passante continuaient à se développer. Cela a pratiquement assuré une période de chevauchement entre les deux normes, rendant ainsi les similitudes en matière de conception et de pratiques de test essentielles à une transition harmonieuse.

Mises à jour de la couche physique du PCIe 5.0

En plus des exigences plus rigoureuses en matière de gigue, des contraintes de budget en perte de canaux et des exigences de marge de voie pour la tension et le délai qui accompagnaient la sortie de la norme PCI Express Gen 5, l’augmentation de la vitesse exigeait des changements supplémentaires au niveau de la couche physique, tandis que d’autres avancées étaient incluses afin de conserver la rétrocompatibilité avec les versions antérieures de la norme PCIe.

Les changements d’ensemble ordonné représentaient par ailleurs une importante modification accompagnant le lancement de la spécification PCI Express 5.0. L’ensemble ordonné EIEOS est utilisé pour faciliter la sortie d’un état de veille électrique. Le schéma familier à seize zéros et uns, utilisé pour chaque paire ordonnée du PCIe 4.0, est devenu un schéma à trente-deux zéros et uns répétés pour chaque voie dans la convention du PCIe Gen 5. Les signaux EIEOS (répétés) consécutifs représentent un autre changement au sein du protocole PCIe 5.0. L’ensemble ordonné de début de streaming de données (Start of Data Stream, SDS) a lui aussi été mis à jour pour que les points d’origine de streaming des données du PCI Express Gen 5 puissent être clairement reconnus par le récepteur.

Les séquences de formation (TS1/TS2) ont bénéficié de nouvelles options innovantes, conçues pour faciliter le doublement de la vitesse du PCIe Gen 5. Les séquences de formation sont un précurseur nécessaire à l’ajout de lien et à l’égalisation (EQ), mais elles peuvent aussi causer des délais lorsque les ensembles ordonnés passent par chaque incrément de prise en charge du débit, en commençant par 2,5 GT/s pour atteindre par étape une vitesse de 32,0 GT/s pour le PCIe Gen 5. Pour remédier à ce dilemme, des options de dérivation d’égalisation ont été fournies, permettant de « sauter » les niveaux d’égalisation de vitesse intermédiaires ou pour les omettre tout simplement à l’aide de l’option « Absence d’EQ » pour permettre une transmission immédiate vers l’état de transfert de données L0 actif.

De nouveaux domaines d’identification de protocoles alternatifs et une prise en charge améliorée du précodage ont également été ajoutés aux TS1 et TS2 modifiés du PCIe Gen 5. Une fois que la négociation entre l’appareil et le système a réussi, la liaison peut immédiatement passer à l’état L0 à la vitesse la plus élevée prise en charge et entamer le transfert de données en utilisant le protocole alternatif négocié. Dans le cas d’un échec de la négociation avec un protocole alternatif, le système peut rapidement revenir au protocole de base du PCIe 5.0.

La variété presque illimitée des conditions et scénarios de liaison rend difficile la recherche de panne lors de la phase d’ajout (pré-L0) et des phases actives (L0) de l’activité d’une liaison PCIe 5.0. Les meilleures solutions de test du PCIe Gen 5 permettent une approche systématique, par couche, qui réduit de manière considérable le temps et les efforts liés à la recherche de panne, tout en améliorant les mesures de performance continues du système.

Les problèmes d’ajout de liaison observés durant l’état LTSSM (Link Training and Status State Machine) comprennent les problèmes de détection et d’intégrité du signal, les vitesses de liaison incorrectes et d’autres conditions potentielles pouvant être diagnostiquées de manière efficace à l’aide d’un analyseur de protocole. Une fois l’état L0 atteint, les performances inadéquates dues, par exemple, à des répétitions excessives, à des problèmes de récupération et à des retards au niveau de différentes couches de la pile de protocoles, peuvent également être détectées et atténuées efficacement avec l’aide d’un analyseur de protocole PCIe avancé.

Une condition de couche physique courante exigeant une capacité de diagnostic précis apparaît lors de la sortie de l’état de veille électrique, lorsque des incompatibilités entre les logiques de l’émetteur et du récepteur peuvent créer de la latence. Le Xgig Analyzer de VIAVI identifie ces conditions de manière fiable en employant des durées de verrouillage courtes et des capacités de post-traitement avancées, minimisant ainsi la perte de données capturées durant les transitions d’état à faible alimentation.

Il est très important de disposer de mesures en temps réel pour la couche physique afin de contrôler l’état général du signal et les données de récupération des liaisons. Par exemple, lorsque la liaison fonctionne à l’état L0, les retransmissions et les récupérations répétées, qui créent potentiellement une baisse importante de la performance du système, passent souvent inaperçues. Les fonctionnalités de surveillance en temps réel, de mesures et d’analyse post-capture effectuées par Xgig avec une résolution par voie contrôlent et diagnostiquent de manière efficace les accusés de réception négatifs (NAK), les retransmissions, les erreurs de liaison et les statistiques de contrôle de flux (FC) telles que les débordements de tampon récepteur et les profondeurs de file d’attente excessives.

La cadence effrénée des dates de lancement des normes PCIe semble devoir continuer, avec le lancement de la spécification finale du PCIe 6.0 prévu pour 2021. Cette nouvelle version continuera de doubler comme à chaque fois la bande passante et offrira une fois de plus la rétrocompatibilité propre à la norme PCIe, pour atteindre cette fois l’impressionnant record de 256 Go/s de bande passante bidirectionnelle. Dans les faits, cela placera le PCIe au niveau de la bande passante VRAM d’un processeur graphique bas de gamme.

Afin de permettre un nouveau doublement du débit et de conserver les normes de haute fiabilité, les technologies de modulation d’impulsions en amplitude (PAM4) et de correction d’erreur sans voie de retour (FEC) seront utilisées. L’intelligence artificielle et l’apprentissage machine pourront potentiellement bénéficier de cette amélioration, car leurs performances se fondent sur une combinaison de vitesse exceptionnelle, de faible latence et d’accès rapide et simultané à de multiples périphériques.

Le PCIe Gen 5 constitue ainsi une avancée réussie de plus dans la technologie des bus d’E/S. Il semble que la spécification PCIe 5.0 parviendra à maintenir la cadence imposée par la loi de Moore tout en supprimant le goulet d’étranglement de l’architecture de réseau dans un avenir proche. Avec l’arrivée continue d’outils de test PCIe 5.0 nouveaux et améliorés, cette progression devrait se poursuivre avec succès avec le lancement du PCIe 6.0 et des nombreuses générations à venir.

Suivi à chaque étape

Nous assurons l’assistance, les services, des formations complètes ainsi que les ressources qu’il vous faut. Tout cela dans le but de maximiser la valeur de vos investissements VIAVI.

Interrogez un expert

Contactez-nous pour de plus amples informations ou pour recevoir un devis. Nos experts sont là pour répondre à toutes vos questions.