计算快速链路 (CXL)

计算快速链路指南和资源

计算快速链路技术正在快速发展,以解决人工智能和机器学习应用程序带来的内存分配和数据存储挑战。VIAVI 的高级分析解决方案帮助运营商支持 CXL 标准的独特测试和验证要求。

产品

-

适用于 PCI Express 6.0 的 Xgig 6P16 分析仪/协议训练器

完全集成的 16 通道 PCIe6 分析仪/协议训练器解决方案,支持 CXL 和 NVMe

-

适用于 PCI Express 5.0 的 Xgig 5P16 分析仪 / 协议训练器 / 干扰器平台

在同一平台上结合了分析仪、协议训练器和干扰器功能,并支持最新的 PCIe、NVMe 和 CXL 规范,以及同步多用户分析仪功能

-

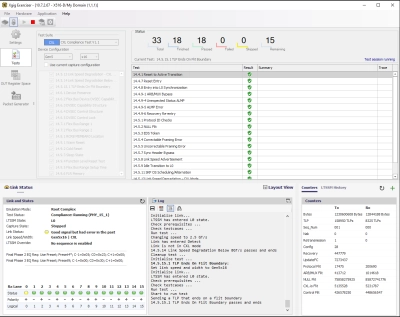

适用于 CXL v1.1/v2.0 的 Xgig 协议训练器

CXL 协议训练器获准用于 CXL 黄金套件合规性测试,能够以 32 GT/秒的速度生成 CXL 数据流量和响应,用于合规性性测试和分析

作为 CXL 联盟的参与成员,VIAVI 已经认识到围绕计算快速链路拓扑的行业共识正在不断增长。数十年的高速互连测试经验使 VIAVI 有资格领导重要的 CXL 解码验证工作,并从以客户为中心的角度参与正在进行的规范开发。

业界领先的 PCIe® 协议分析仪、干扰器、协议训练器和测试软件产品组合跨越了多代标准,使 VIAVI 能够在同一物理接口上自然地转向 CXL 测试流程。CXL 提升的实时指标、交易分析以及详细的捕获和分析现在可以在多功能和直观的测试平台中使用。

每一阶段的支持

我们提供您所需的支持、服务、全面培训以及资源。这只是我们为最大程度提升您投资的价值所作努力的一部分。

咨询专家

请与我们联系以了解详细信息或获取报价。不管您有任何疑问,都可以咨询我们的专家来获得正确解答。