PCIe 5.0

多功能机箱提高了工具生产率并降低了总拥有成本

PCIe 5.0 的速度是 PCIe 4.0 的两倍,同时仍然保持向下兼容。PCIe Gen 5 协议分析仪能够支持 32GT/秒的数据链路速度操作,同时具有卓越的内存、存储容量和分段功能,可捕获更大容量的上行和下行流量。

产品

-

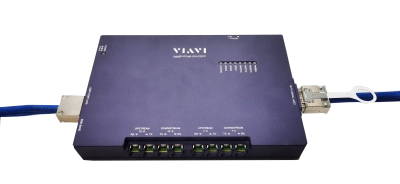

适用于 PCI Express 5.0 的 Xgig 5P16 分析仪 / 协议训练器 / 干扰器平台

在同一平台上结合了分析仪、协议训练器和干扰器功能,并支持最新的 PCIe、NVMe 和 CXL 规范,以及同步多用户分析仪功能

-

适用于 PCI Express 5.0 的 Xgig 5P8 分析仪 / 协议训练器 / 干扰器平台

提供全速 32 Gbps 数据捕获,支持对 PCIe 协议进行详细的功能和性能分析以及同步多用户功能

-

适用于 PCI Express 5.0 的 Xgig 协议训练器主机测试台接口适配卡模块

PCIe 协议训练器主机测试台为 PCIe 适配器卡端点提供连接和电源,以进行测试和验收。

-

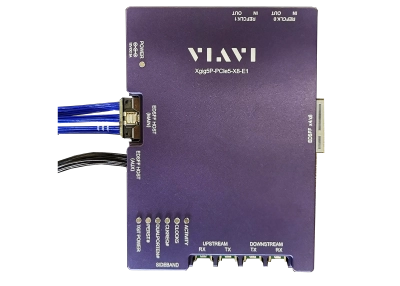

Xgig E1 EDSFF 8-Lane Interposer for PCI Express 5.0

The Xgig® 5P-PCIe5-X8-E1 Interposer is optimized for developing, debugging and performance-tuning NVMe SSD operation...

-

适用于 PCI Express 5.0 的 Xgig E3 EDSFF 16 通道接口适配卡

Xgig5P-PCIe5-X16-E3 接口适配卡针对高密度存储服务器中 NVMe SSD 操作的开发、调试和性能调整进行了优化

-

适用于 PCI Express 5.0 的 Xgig CEM 16 通道接口适配卡模块

PCIe 5.0 16 通道 CEM 接口适配卡可以调试和验证新的 IC、新的系统硬件设计、FPGA 固件以及验证系统 BIOS 和软件。

-

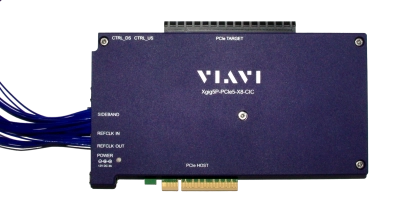

Xgig CEM 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

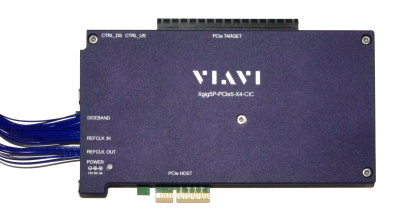

Xgig CEM 4-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 4-lane CEM Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

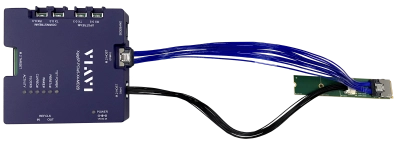

Xgig M.2 4-lane Interposer Module for PCI Express 5.0

The Xgig M.2, 4-lane Interposer for PCI Express® 5.0 is an Active Interposer with a design optimized for M.2 SSD...

-

适用于 PCI Express 5.0 的 Xgig U.2-Server 4 通道接口适配卡模块

Xgig® U.2-Server 接口适配卡针对 NVMe SSD 在具有 U.2 连接的高密度存储服务器中的开发、调试和调整进行了优化

-

适用于 PCI Express 5.0 的 Xgig U.3-Server 4 通道接口适配卡模块

Xgig® U.3-Server 接口适配卡针对 NVMe SSD 在具有 U.3 连接的高密度存储服务器中的开发、调试和调整进行了优化

-

Xgig Slimline 8-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 8-lane Slimline Interposer enables debug and verification of new ICs, new system hardware designs, FPGA...

-

Xgig CDFP 16-lane Interposer for PCI Express 5.0

This PCIe 5.0 16-lane CDFP/CopprLink™ Interposer provides a tap of PCIe data signals between two externally cable-...

-

Xgig OCP3 16-lane Interposer Module for PCI Express 5.0

The PCIe 5.0 16-lane OCP3 Interposer provides a tap of host-system PCIe signals to OCP NIC 3.0 devices for input...

-

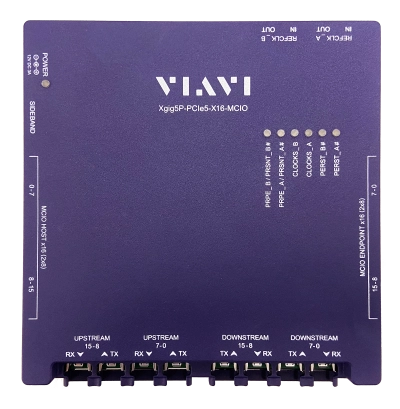

适用于 PCI Express 5.0 的 Xgig MCIO 16 通道接口适配卡模块

PCIe 5.0 16 通道 MCIO/CopprLink™ 接口适配卡支持对 16 通道 MCIO/CopprLink™ 主机端口和 MCIO/CopprLink™ 连接端点设备之间的通信进行协议分析。

-

适用于 PCI Express 5.0 的 Xgig 飞线 4 通道探针

提供被测设备和 VIAVI 协议分析仪机箱之间的数据信号连接

-

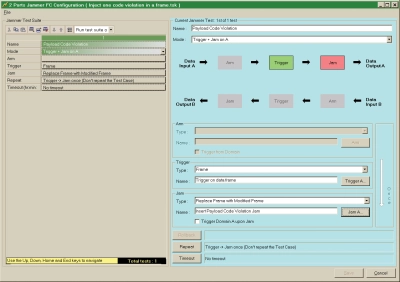

Xgig 干扰器

Xgig® 干扰器能够操纵实时网络流量,模拟实时错误,使用户能够验证错误恢复程序的响应速度和稳定性。

-

适用于 PCI Express 5.0 的 Xgig 协议训练器

PCIe 协议训练器生成 PCIe 数据流和响应,用于合规性测试和分析 PCIe 5.0 协议。

-

适用于 CXL v1.1/v2.0 的 Xgig 协议训练器

CXL 协议训练器获准用于 CXL 黄金套件合规性测试,能够以 32 GT/秒的速度生成 CXL 数据流量和响应,用于合规性性测试和分析

-

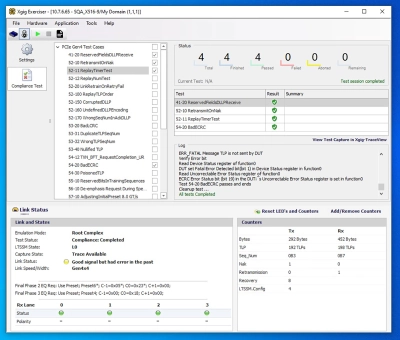

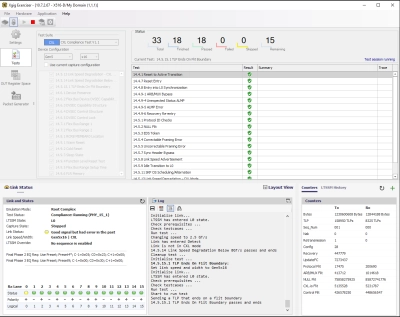

Xgig Expert

Expert 软件的标准配备带有所有 Xgig 分析仪,是一个独特而强大的调试和分析套件,专为加速和简化设备开发和故障排除程序设计。

-

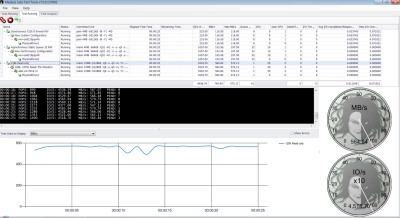

Medusa Labs Test Tools Suite

Medusa Labs Test Tools Suite 是基于应用的领先数据测试和信号完整性测试工具,使开发者能够在产品上市之前通过压力测试识别、定位和解决难以捉摸的错误。

随着数据速率的显著提高,测试标准和实践继续受到每个新的 PCIe 版本的挑战,PCIe Gen 5 也不例外。例如,修订后的电气空闲退出有序集 (EIEOS) 和时钟功能已经影响了硬件和系统级别的测试实践。

替代协议也需要全面的测试支持,因为这种改进的多功能性现在允许其他协议利用成熟的 PCIe 物理层堆栈。

- Compute Express Link (CXL) 是行业支持的高速缓存一致性互连,适用于处理器、内存扩展和加速器

- NVM Express® (NVMe®) 定义了主机软件如何通过 PCI Express® (PCIe®)、RDMA、TCP 等多种传输协议与非易失性存储器进行通信。它是所有外形规格(U.2、M.2、AIC、EDSFF)的固态硬盘 (SSD) 的行业标准。

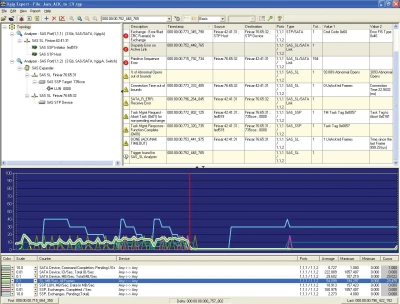

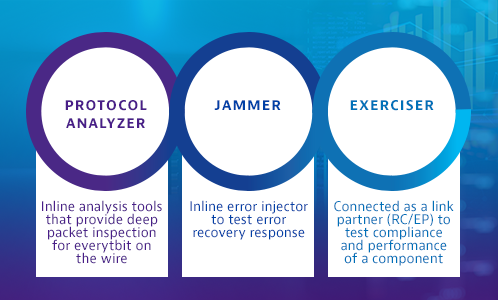

Xgig 分析仪

完全向下兼容的协议分析仪能够支持 32GT/秒的数据链路速度操作,例如 VIAVI Xgig 分析仪,对于执行最新的 PCIe 5.0 测试和调试过程非常宝贵。卓越的内存、存储容量和分段功能可实现更大容量的上行和下行流量捕获,从而可以记录长序列,并过滤掉特定的数据包,以便进行可靠的协议分析。查看所有协议分析仪。

Xgig 协议训练器

适用于 PCIe 5.0 的 VIAVI Solutions Xgig® 协议训练器为 Xgig PCIe 产品组合带来了交钥匙合规性测试功能。

- 用于调试疑难协议通信问题的有用工具,因为它能够提供对 PCIe 数据流量的全面、位级、可重复的控制。

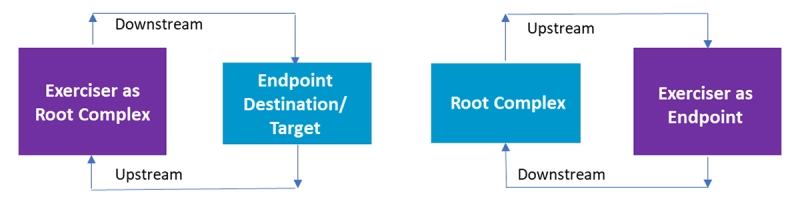

- 取代通信链路合作伙伴,并提供对根联合体或端点测试的完全控制,如图所示

- 组件级分析和调试的理想之选

协议训练器有两种操作模式。主机或根联合体模式(左)用于测试端点。

端点模式(右)用于测试主机系统、交换机端口和 CPU。

Xgig 协议训练器经外围组件互连特别兴趣小组 (PCI-SIG) 批准,可用于 PCI Express (PCIe) 4.0 协议合规性认证测试,该测试在 PCI-SIG 合规性研讨会上进行。PCIe 4.0 是目前由 PCI-SIG 执行的最高级别的合规性认证。查看所有协议训练器。

Xgig 干扰器

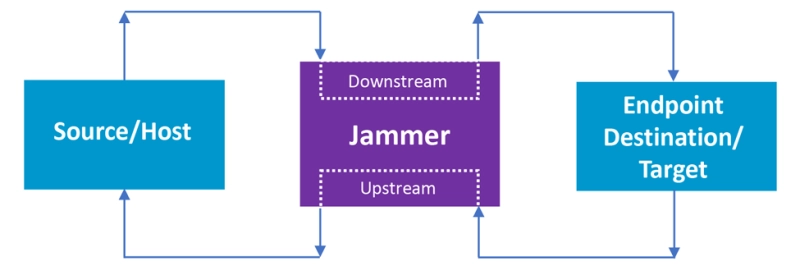

干扰器在 CPU 和端点之间以串联方式运行,并在实际系统设备之间的通信中注入错误。查看所有干扰器。

- 最适合系统测试和错误恢复分析。

- 网络流量的实时模拟为 PCIe 5.0 硬件提供了一个重要的试金石

- 有助于确保设备在真实环境中完全按照需要的方式运行

- 对任务关键型产品至关重要。

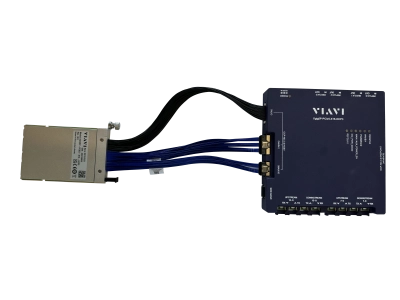

接口适配卡

接口适配卡能够捕获主机系统和被测设备 (DUT) 之间的通信。VIAVI 提供全系列受欢迎的 PCIe 接口适配卡,其中包括:

- 主机测试台

- CEM

- EDSFF、E1、E3

- U.2、U.3

- U.2 CEM

- M.2

- SFF-8674

- 飞线

- Oculink Slimline

Xgig 工具套件

Xgig 工具套件支持 Xgig PCIe 5.0 平台,其中包括:

- Xgig Expert™ 是一个用户友好的界面,有助于快速数据解释、性能分析和故障排查。

- Xgig Serialytics™ 构建于 Xgig Expert 之上,在轨线中公开隐藏的行为和事件。它增强了上下文调试,并为串行协议提供了智能分析

- Xgig Trace Control 是操作员用于配置系统以进行测试的系统设置用户界面

- Medusa Labs Test Tools Suite (MLTT) 是基于应用的数据和信号完整性测试工具,使开发者能够通过压力测试识别、定位和解决错误。

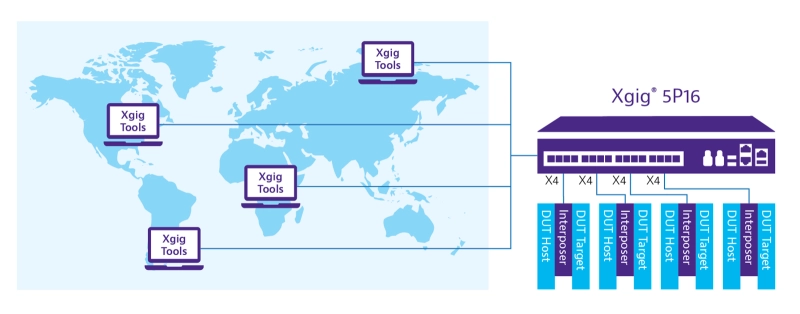

传统上,PCI Express® 协议分析是由一个用户在专用的单功能设备上进行单次测试来执行的。现在,多个用户可以同时登录一台 VIAVI Xgig® 5P16 或 5P8 分析仪,进行同步独立测试。

分叉支持同时多用户 (SMU) 灵活性

用户也不必与分析仪在同一个物理位置。如果他们可以访问网络,则可以从世界上的任何地方远程登录。下图是一个 16 数据通道分析仪的例子,分为四个独立的链路,供多个用户分别进行同步测试。

分叉的工作原理是将通常为一条链路的端口分成两条或多条链路。如下图所示,VIAVI Xgig 5P8 可分为两条 4 数据通道链路,5P16 可分为两条 8 数据通道链路或四条 4 数据通道链路。

Xgig 5P16 机箱还支持分析仪、协议训练器和干扰器功能

我们的旗舰系统 Xgig 5P16 在同一个机箱上支持全功能分析仪、协议训练器和干扰器功能。像这样灵活的软件定义平台简化了设备管理。与硬件模块相比,软件升级可以更快、更经济地提供,并且可以随时添加,使经理能够节省资金,直到需要升级为止

设备生产效率的提高缩短了上市时间,降低了总体拥有成本

Xgig 多功能分析仪创造了单一功能设备难以企及的操作效率。这使用户能够简化配置和调试过程,从而使产品和组件更快地通过测试并推向市场。

通过 PCI-SIG 认证测试

Xgig 协议训练器经外围组件互连特别兴趣小组 (PCI-SIG) 批准,可用于 PCI Express (PCIe) 4.0 协议合规性认证测试,该测试在 PCI-SIG 合规性研讨会上进行。PCIe 4.0 是目前由 PCI-SIG 执行的最高级别的合规性认证。VIAVI 积极参与 PCI-SIG,支持 PCIe5 合规性测试。

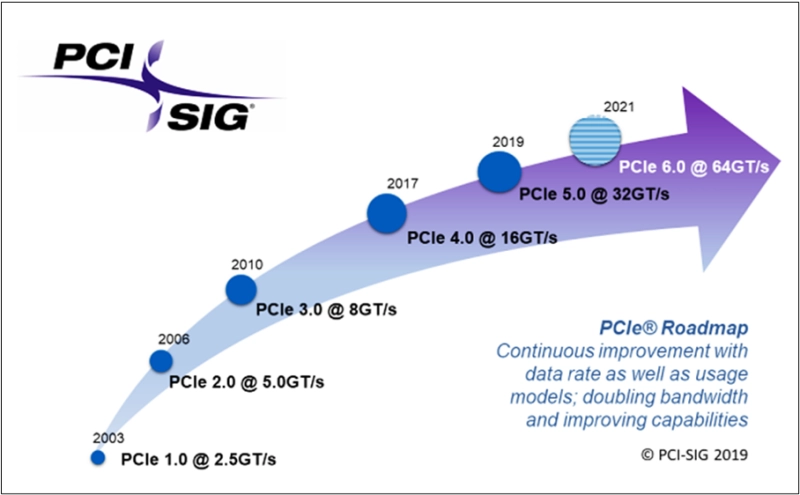

2019 年发布的 PCI Express 5.0 标准的最终版本是加速的 18 个月开发周期的高潮,该周期被认为是解决数据密集型应用程序不断增长的性能需求所必需的。

和所有前几代一样,PCIe 5.0 保持了与过去迭代的向后兼容性,尽管 PCIe 插槽和连接卡之间的最低版本(速度)仍然是制约因素。除了带宽增加之外,PCIe 5.0 规范还包括提高信号完整性的电气增强和提高连接器性能的机械更新。

与每个连续的 PCIe 版本一样,PCIe Express 5.0 和以前的 PCIe 版本之间的共存(通过 PCIe 接口的固有向后兼容性实现)允许云计算和人工智能 (AI) 等要求最高的高性能应用利用最高的可用传输速率,而前几代技术仍在为要求较低的应用使用。

2019 年 PCIe 5.0 的发布日期只是实施过程中的众多渐进步骤的第一步。初步的合规性和互操作性测试也必须成功完成。这些额外的里程碑可能会将第一批经认证的 PCIe 5.0 商用产品的推出时间推迟至将来。

由于 PCIe 已集成到当今使用的几乎所有类型的计算系统中,PCI Express 5.0 的共生客户和供应链基础设施包括电子、计算、数据存储和电子商务行业中的许多世界上最大的公司。这包括支持 PCIe Gen 5 功能的知识产权 (IP) 供应商、交换机和重定时器制造商,以及 PCIe 5.0 主板、存储设备和图形控制器供应商。这些重要的构建模块为数据中心和其他基础网络部署提供了先进的计算机系统和硬件。

PCIe 5.0 早期采用的细分市场

预期并非所有企业和细分市场将同时采用 PCI Express Gen 5 技术。IP 市场将需要早期验证功能,以确保 FPGA 或硅格式的功能。CPU、以太网和精选加速器细分市场也将在 PCIe 5.0 的早期推广中发挥重要作用。数据中心服务器和高性能计算 (HPC) 基础设施已经在努力满足不断增长的带宽和延迟需求,一旦 PCIe Gen 5 技术面世,它们将迅速吸收其固有优势。

PCIe 5.0 协议分析用户

更短的验证和调试周期对于加快上市时间至关重要。这为执行验证和确认的系统集成团队以及致力于鉴定组件和解决互操作性问题的调试团队创造了对高级 PCIe Gen 5 协议分析工具的更大需求。设备、驱动程序和应用软件的性能调优团队也从先进的 PCIe 5.0 协议分析功能中获得了丰厚的投资回报。

PCIe 的速度倍增减惯例与 PCIe 5.0 的发布保持一致。PCIe 5.0 使用自 PCIe 3.0 版以来的标准 128b/130b 编码方法,将在每个方向上提供 64 GB/秒的吞吐量。由于 PCIe 技术允许数据全双工双向流动,因此两个方向的总吞吐量加起来达到 128 GB/秒。

PCIe 3.0 之前的编码标准是 8b/10b,这意味着 8 位数据被编码并作为 10 位数字传输。这进而产生了 20% 的性能开销因子,将 2.5 GT/秒的原始比特传输速率降低到仅为 2.0 Gbit/秒的净带宽。这个更有效的 1.5% 开销因子在 PCIe 5.0 编码惯例中仍然有效。

PCIe 版本 |

发布 年份 |

传输速率 |

吞吐量/数据通路 |

x16 吞吐量 |

1.0 |

2003 年 |

2.5 GT/秒 |

250 MB/秒 |

4.0 GB/秒 |

2.0 |

2007 年 |

5.0 GT/秒 |

500 MB/秒 |

8.0 GB/秒 |

3.0 |

2010 年 |

8.0 GT/秒 |

1.0 GB/秒 |

16.0 GB/秒 |

4.0 |

2017 年 |

16.0 GT/秒 |

2.0 GB/秒 |

32.0 GB/秒 |

5.0 |

2019 年 |

32.0 GT/秒 |

4.0 GB/秒 |

64.0 GB/秒 |

PCIe 5.0 的惊人速度使得相当于一个典型蓝光光盘的内容能够在不到一秒钟的时间内传输到 PCI 5.0 主板上的非易失性存储器 (NVM)。尽管这种超乎寻常的速度看起来像是奢侈品,但这是其他领域的网络架构增强所必需的。例如,400G 以太网在每个方向上需要 50 GB/秒的带宽才能以最大容量与 CPU 连接。

对于 PCIe 4.0,全尺寸 x16 插槽上可用的 32 GB/秒已被证明是不够的。使用 PCIe 5.0 技术,可用带宽超过了该接口的要求,还有剩余空间。

除了以太网之外,这种持续改进周期的推动因素是具有延迟关键型性能要求的实时系统的出现,例如自动驾驶、需要即时响应的防御应用,以及必须立即挫败黑客企图的关键金融安全应用。多 GPU 系统和高级显卡的个人用户也可以从 PCIe 5.0 的速度和带宽增强中获得实实在在的好处。

PCIe 5.0 规范可以被归类为向后兼容的 PCIe 标准的自然演进,在这个迭代中不包括固有的链路或事务层变化。PCIe 5.0 规范继续受益于 PCIe 4.0 建立的缩放流量控制以及扩展标记和信用。

还添加了一个新的指定用于附加卡的 CEM 连接器。信号完整性和连接器设计特性的改进提高了整体性能和可靠性。物理层增强还包括对 EIEOS、SKP 有序集和均衡序列的更新。

PCI Express 5.0 规范受到硬件制造商和业内人士的普遍好评。特别是,为提高可测试性、加速链路训练和提供备用协议支持而进行的增强被认为是 PCIe 5.0 的突出特点。这一行业共识,以及从 PCIe 4.0 过渡到 PCIe 5.0 所需的一组相对温和的实施先决条件,引领了积极的硬件开发和商业化目标。

伴随 PCIe 5.0 发布而来的改进和规范更改进一步放大了许多 PCIe 架构挑战,使测试和开发活动变得复杂化。这包括将发射器(发射)抖动降低 2 倍的要求和将参考时钟抖动降低 3 倍的要求。

在 PCIe 5.0 中,信号丢失仍然是一个持续的架构挑战。重定时器、重驱动器和替代印刷电路板 (PCB) 基材是硬件设计人员可用来减轻这些问题的一些具有成本效益的选项。可以使用重定时器来重新传输信号,也可以使用重驱动器来放大信号,这两种方法都可以提高链路的物理覆盖范围。

PCI Express 5.0 规范定义的信道损耗预算为 36db,仅比 PCIe 4.0 阈值高出约 28%。PCIe 技术固有的插入损耗在 PCIe 5.0 版本中继续存在,因此 FR4 PCB 结构所经历的损耗水平已不再适用,而像 MEGTRON 这样的替代材料(成本高达 FR4 的 2.5 倍)已成为强制性材料。PCI Express 5.0 的信道要求也要求为发射器(发射)和接收器(接收)设计新的均衡电路,并且电压和定时的接收通道裕度已成为强制要求。

在从 PCIe 4.0 到 PCI Express 5.0 的过渡中,速度翻倍、向后兼容和加速发布周期是构建实施策略的三个基本支柱。

启用或支持提速的新功能优先于其他建议或请求的更改。例如,需要更改 EIEOS 和数据比特率定义才能实现速度提升,但编码方法和目标比特误码率 (BER) 等基本 PCIe 元素保持不变。信令和加扰方案也与 PCIe Gen 4 保持一致,并在可能的情况下利用现有的发射器(发射)和接收器(接收)测试方法将实施影响降至最低。

尽管强调上市时间和兼容性,PCIe 4.0 和 PCIe 5.0 之间的其他重要设计更改必然会影响配套硬件和测试实践。其中包括具有二阶响应的时钟数据恢复 (CDR) 和仅与表面贴装 PCBA 封装兼容的 CEM 连接器,尽管它在附加卡接口处保持向后兼容。PCI Express 5.0 还通过修改的 TS1/TS2 序列支持替代协议。

PCIe 4.0 和 PCIe 5.0 标准之间的一致性因 4.0 标准的发布时间过长而变得更加必要,因为网络环境和带宽需求继续在后台展开。这实际上保证了两个标准之间的重叠期,使得设计和测试实践的通用性对于平稳过渡至关重要。

PCIe 5.0 物理层更新

除了 PCI Express Gen 5 版本附带的更严格的抖动要求、信道损耗预算约束以及通道电压和时间裕度要求外,速度提高还需要额外的物理层更改,同时还包括其他改进,以保持与以前的 PCIe 版本所需的向后兼容性。

有序集更改是 PCI Express 5.0 规范版本附带的一项重要修改。EIEOS 有序集用于帮助退出电气空闲状态。在 PCIe Gen 5 惯例中,用于每个 PCIe 4.0 有序对的熟悉的 16 个 0 和 1 的模式变成了对每个通道重复的 32 个 0 和 1。背靠背(重复)EIEOS 信号是 PCIe 5.0 协议的额外更改。数据流起始有序集 (SDS) 也已更新,因此接收方可以清楚地区分 PCI Express Gen 5 数据流起始点。

训练序列 (TS1/TS2) 受益于旨在促进 PCIe Gen 5 速度倍增的创新新选项。训练序列是链路建立和均衡 (EQ) 的必要先导,但随着有序集通过每个速度支持增量(从 2.5 GT/秒开始并逐步移动到 32.0 GT/秒 PCIe Gen 5 速度),训练序列也可能导致延迟。为了解决这个难题,提供了EQ 旁路选项,以基本上“跳过”中间速度均衡级别,或者通过使用“无 EQ”选项立即转换到 L0 活动数据传输状态来完全省略均衡。

PCIe 5.0 的改进型 TS1 和 TS2 也增加了新的字段,用于替代协议 ID 和增强的预编码支持。一旦系统和设备之间的协商成功,链路就可以立即以支持的最高速度进入 L0 状态,并开始使用协商的备用协议传输数据。如果替代协议协商失败,系统可以快速恢复到骨干网 PCI Express 5 协议。

在 PCIe 5.0 链路活动的启用(L0 之前)阶段和完全启用 (L0) 阶段,几乎任意数量的不同的链路条件和场景都会带来故障排查挑战。最好的 PCIe Gen 5 测试解决方案支持分层、系统化的方法,可显著减少故障排查时间和工作量,同时改进持续的系统性能指标。

在链路训练和状态状态机 (LTSSM) 状态期间观察到的链路启用问题包括信号完整性和检测问题、不正确的链路速度以及可以使用协议分析仪有效诊断的其他潜在情况。在达到 L0 状态后,在高级 PCIe 协议分析仪的帮助下,还可以有效地检测和缓解协议栈各层的性能低效,例如重放过多、恢复问题和延迟。

需要精确诊断能力的一种常见 PHY 层条件是在从电空闲状态退出期间,此时发射和接收逻辑之间的不匹配会引起延迟。VIAVI Xgig 分析仪 通过采用较短的锁定时间和高级后处理功能可靠地识别这些情况,从而最大限度地减少低功耗状态转换期间捕获的数据丢失。

物理层的实时指标对于监控整体信号健康状况和链路恢复数据极其重要。例如,当链路运行在 L0 状态时,重复的重放和恢复可能会导致系统性能显著下降,但通常不会被检测到。具有每通道分辨率的 XGIG 实时监控、指标和捕获后分析功能可有效监控和诊断非确认 (NAK)、重放、链路错误和流量控制 (FC) 统计数据,例如接收器缓冲区溢出和过大的事务队列深度。

PCIe 发布日期的惊人节奏似乎注定会延续,预计将于 2021 年发布 PCIe 6.0 的最终规范版本。这一新的迭代将继续传统的带宽加倍和向后兼容,这意味着 PCIe 标准这一次达到了令人震惊的 256 GB/秒的双向带宽。这将有效地将 PCIe 与低端 GPU 的 vRAM 带宽相媲美。

为了使速度再提高两倍并保持高可靠性标准,将采用脉冲幅度调制 (PAM4) 和前向纠错 (FEC) 技术。人工智能和机器学习是这一增强的潜在受益者,因为它们的性能依赖于卓越的速度、低延迟和同时快速访问多个外围设备。

PCIe Gen 5 是 I/O 总线技术的又一次成功飞跃。在可预见的未来,PCIe 5.0 规范似乎将遵循摩尔定律,同时摆脱网络架构瓶颈的束缚。随着每天都有新的和改进的 PCIe 5.0 测试工具面世,这一进展应该会通过 PCIe 6.0 和未来许多代的发布成功地继续下去。

每一阶段的支持

我们提供您所需的支持、服务、全面培训以及资源。这只是我们为最大程度提升您投资的价值所作努力的一部分。

咨询专家

请与我们联系以了解详细信息或获取报价。不管您有任何疑问,都可以咨询我们的专家来获得正确解答。