PCIe 4.0

Erweiterte Analyse- und Jamming-Funktionen mit branchenführender Signalintegrität und automatischer Abstimmung

Produkte

-

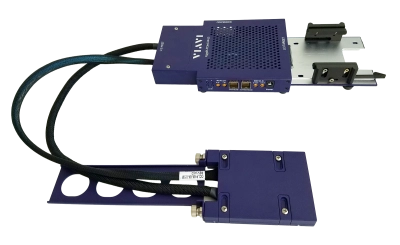

Xgig 4K16 Analyzer / Jammer Platform for PCI Express 4.0

The most powerful PCIe Gen 4.0 analysis system available, offering complete visibility into traffic flows with…

-

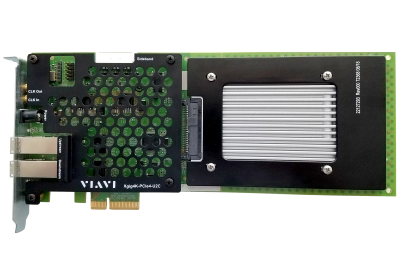

Xgig 4K4 Analyzer Platform for PCI Express 4.0

The Xgig 4K4 platform provides protocol analysis for PCIe and NVMe traffic at all layers of the stack

-

Xgig E1 EDSFF Interposer Module for PCI Express 4.0

Xgig4K-PCIe4-X8-E1 is an Active Interposer optimized for developing, debugging and performance tuning NVMe SSD…

-

Xgig CEM Type-B, 16-lane Interposer Module for PCI Express 4.0

The PCIe 4.0 16-lane CEM Type-B Interposer enables debug and verification of new ICs, new system hardware designs,…

-

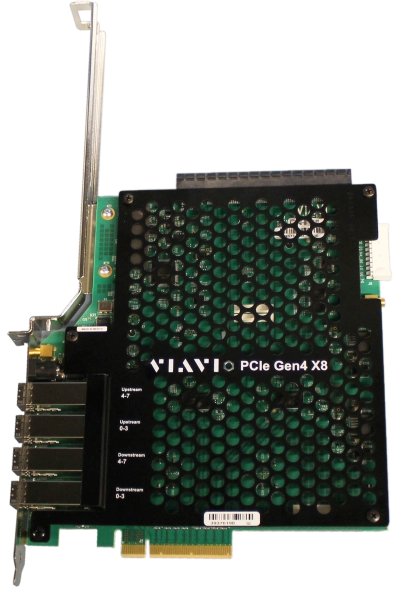

Xgig CEM, 8-lane Interposer Module for PCI Express 4.0

The PCIe4, 8-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA…

-

Xgig CEM-slot, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA…

-

Xgig U.3-Server, 4-lane Interposer Module for PCI Express 4.0

Provides a tap of communication between a host-system and a U.3 NVMe SSD for input to the VIAVI PCIe 4.0 Analyzer…

-

Xgig U.2B-Server, 4-lane Interposer Module for PCI Express 4.0

This U.2-Server, version B Interposer is optimized for development, debugging and tuning of NVMe SSD operation in…

-

Xgig U.2-CEM, 4-lane Interposer Module for PCI Express 4.0

This U.2-CEM Interposer is optimized for NVMe SSD development enabling debug and analysis

-

Xgig M.2, 4-lane Interposer Module for PCI Express 4.0

The M.2, 4-lane Interposer for PCI Express® 4.0 is an Active Interposer with a design optimized for M.2 SSD…

-

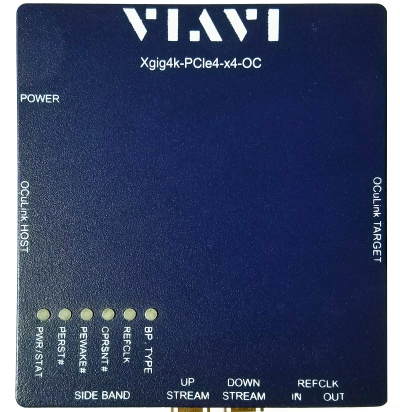

Xgig Oculink, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane OCulink/Slimline Interposer enables debug of new ICs, hardware designs, FPGA firmware, system BIOS…

-

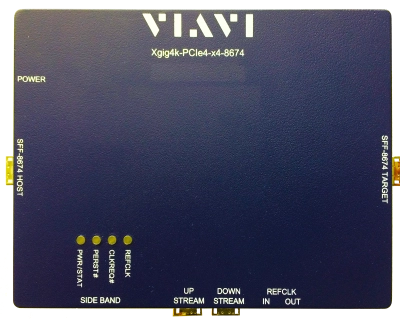

Xgig SFF-8674, 4-lane Interposer Module for PCI Express 4.0

The SFF-8674 Interposer enables protocol analysis of PCI Express 4.0 traffic between an SFF-8674 attached host…

-

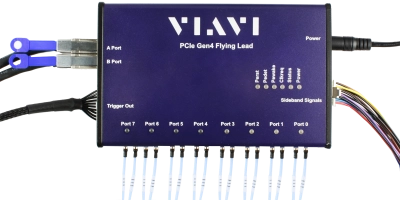

Xgig Flying-Lead, 4-lane Interposer Module for PCI Express 4.0

The Xgig Flying-Lead Interposer captures signals between controller ICs on the same PCB where there is no connector…

-

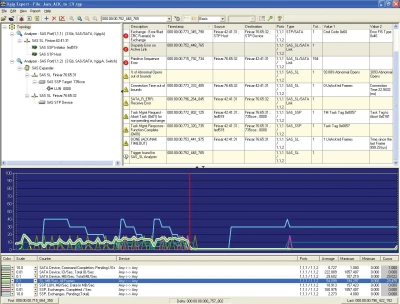

Xgig Expert

Expert software comes standard with all Xgig Analyzers to provide a unique and robust set of debugging and analysis…

-

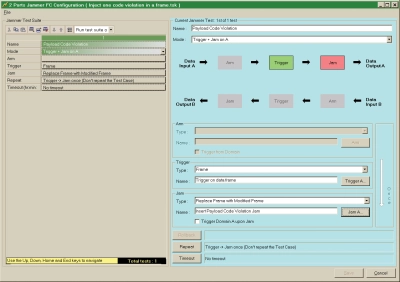

Xgig Jammer for PCI Express 5.0

The Xgig® Jammer manipulates live network traffic to simulate errors in real time, enabling users to verify the…

-

Medusa Labs Test Tools Suite

Medusa Labs Test Tools Suite is the leading application-based data testing and signal integrity testing tool…

Was ist PCIe 4.0?

PCIe 4.0, das auch als PCIe 4, PCIe Gen 4, PCI 4 und PCI Express 4.0 bezeichnet wird, ist die vierte Generation der Highspeed-Bus-Technologie Peripheral Component Interconnect Express (PCIe) für Computer. Sie wurde für Anwendungen entwickelt, die eine größere Bandbreite zu niedrigeren Kosten benötigen. Und wer sich jetzt fragt, ob PCIe 4.0 abwärtskompatibel ist, dem sei gesagt, dass auch diese Version zu allen Vorgängern uneingeschränkt kompatibel bleibt.

Die Spezifikation definiert variable Lane-Breiten von x1, x2, x4, x8, x16 und x32, sodass den Entwicklern nun Breiten- und Raten-Konfigurationen zur Verfügung stehen, mit denen sie Anwendungen mit verschiedenen Bandbreitenanforderungen berücksichtigen können. Beispielsweise verwenden Speicheranwendungen die Lane-Breite PCIe x4, während leistungsstärkere Prozesse, für die größere Bandbreiten wünschenswert sind, von x16 profitieren.

Ein kompatibles PCIe-4.0-Mainboard, das an eine PCIe-4.0-SSD angeschlossen ist, kann eine doppelt so hohe sequenzielle Lese/Schreibgeschwindigkeit wie eine SSD der Vorgängergeneration PCIe 3.0 und mehr als das Zehnfache einiger langsamerer SATA-SSD erreichen.

Die Spezifikation für PCIe 4.0 wurde im Oktober 2017 verabschiedet. Die Transferrate wurde mit 16 GT/s angegeben, was die Rate des Vorgängers PCIe 3.0 verdoppelt. In der untenstehenden Tabelle werden die Bandbreiten-Optionen von PCIe 3.0 mit denen von PCIe 4.0 verglichen.

| Bandbreite in GB/s | PCIe x1 | PCIe x2 | PCIe x4 | PCIe x8 | PCIe x16 |

|---|---|---|---|---|---|

| PCIe 3.0 | 1,97 | 3,94 | 7,87 | 15,75 | 31,51 |

| PCIe 4.0 | 3,94 | 7,87 | 15,75 | 31,51 | 63,02 |

Was ist bei PCIe 4.0 anders?

2003 wurde die erste Generation der PCI-Express-Technologie eingeführt. PCIe 1.0 hat schnell seine direkten Vorgänger PCI und AGP (Accelerated Graphics Port) als Bus-Topologie verdrängt. AGP war damals speziell für Grafikcontroller-Anschlüsse mit höheren Bandbreitenanforderungen entwickelt worden.

Schnell wurden die Vorteile von PCIe gegenüber PCI deutlich, als die serielle Verbindung das alte parallele Format ersetzte und jedes Gerät über einzelne Punkt-zu-Punkt-Verbindungen anstatt über die schwerfällige (geteilte) Shared-Bus-Architektur angeschlossen wurde. PCIe 1.0, das anfangs als High Speed Interconnect bezeichnet wurde, erreichte pro Lane bereits eine Bandbreite von 250 MB/s und eine Transferrate von 2,5 GT/s.

Die 2007 bzw. 2010 verabschiedeten Versionen 2.0 und 3.0 begründeten die mit jeder weiteren PCIe-Generation übliche Verdoppelung der Transferrate. Mit PCIe 3.0 gab es einige schrittweise Verbesserungen, wie der Wechsel des Codierverfahrens von 8b/10b auf 128b/130b. Jede neue PCIe-Generation ist zur Vorgängerversion abwärtskompatibel, wobei die jeweils niedrigere Version und damit Datenrate für die tatsächliche Bandbreitenleistung und Taktrate zwischen PCIe-Slot und Anschlusskarte ausschlaggebend ist.

Bei PCIe 4.0 wurde mit dem bisher üblichen 4-Jahresrhythmus, in dem bis dahin die PCIe-Versionen aufeinander folgten, gebrochen, da dessen Spezifikation erst sieben Jahre nach PCIe 3.0 veröffentlicht wurde. Es hatte sich gezeigt, dass die Entwickler größere Probleme hatten, die mit jeder weiteren PCIe-Generation übliche Verdoppelung der Transferrate bei gleichzeitiger Abwärtskompatibilität der mechanischen und elektrischen Anschlüsse zu gewährleisten.

PCIe 4.0 ist diesen anspruchsvollen Leistungserwartungen nicht nur gerecht geworden, sondern hat auch funktionale Verbesserungen eingeführt. Dazu zählen eine geringere Systemlatenz, die skalierbare Nutzung zusätzlicher Bandbreiten-Lanes sowie das “Lane-Margining“, das heißt die Bewertung der elektrischen Betriebsreserve (Integrität und Zuverlässigkeit) jeder einzelnen Lane des PCIe-Kanals.

Transferraten von PCIe 4.0

Angesichts der unzähligen Verbesserungen, die PCIe 4.0 mit sich gebracht hat, ist es sinnvoll, bei der Aufzählung der zahlreichen Vorteile und neuen Anwendungsmöglichkeiten die deutliche Steigerung der Transferrate als Ausgangspunkt zu nehmen. Die mit jeder Generation erfolgte Verdoppelung der Übertragungsgeschwindigkeit hat dazu geführt, dass PCIe 4.0 mit vier Lanes (x4) den Durchsatz erreicht, für den die erste Generation noch 16 Lanes (x16) benötigte.

In der Praxis ist die neue Transferrate von 16 GT/s mit einem Spannungsschalter vergleichbar, der an einem differenziellen Leitungspaar pro Sekunde 16 Millionen Schaltvorgänge ausführt.

Diese schon traditionelle Verdoppelung der Transferrate hat mit PCIe 4.0 deutliche Kosteneinsparungen bei Highend-Anwendungen, wie Cloud-Server und Rechenzentren, ermöglicht. Gleichzeitig haben sich die Leistung und das Nutzererlebnis verbessert und Einzelgeräte, wie Laptops und Tablets, profitieren von einer deutlichen Effizienzsteigerung.

Trotz der in den vergangenen 16 Jahren verzeichneten, rasanten Steigerungen bei Bitrate und Bandbreite werden noch höhere Übertragungsgeschwindigkeiten benötigt, um mit der Entwicklung der Kernelemente der Netzwerkarchitektur Schritt halten zu können. 400G Ethernet erfordert beispielsweise in jeder Übertragungsrichtung einen Durchsatz von 50 GB/s und übersteigt damit die Möglichkeiten von PCIe 4.0. Da die Busse in der x86-Architektur häufig zum Engpass werden können, warten modernere Anwendungen vielleicht schon auf die von den zukünftigen PCIe-Generationen versprochenen größeren Bandbreiten.

| Version | Transferrate | Durchsatz/Lane | x16-Durchsatz |

|---|---|---|---|

| PCIe 1.0 | 2,5 GT/s | 250 MB/s | 4,0 GB/s |

| PCIe 2.0 | 5 GT/s | 500 MB/s | 8,0 GB/s |

| PCIe 3.0 | 8,0 GT/s | 1,0 GB/s | 16,0 GB/s |

| PCIe 4.0 | 16,0 GT/s | 2,0 GB/s | 32,0 GB/s |

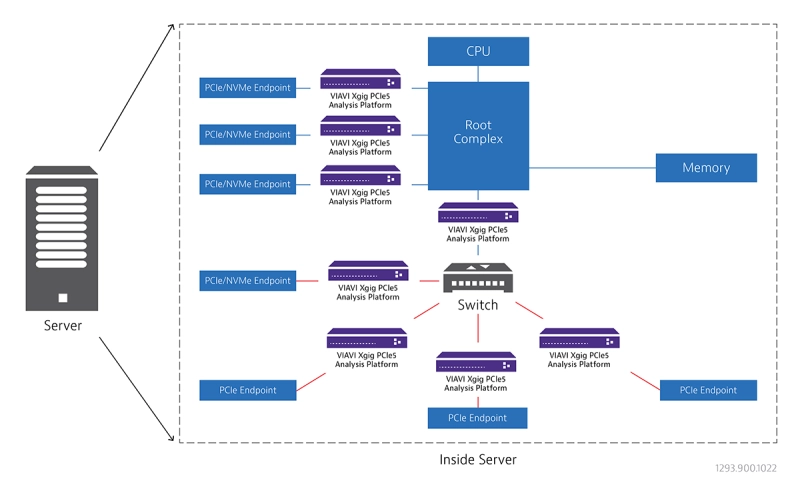

Die Architektur von PCIe 4.0

Die Architektur von PCIe 4.0 soll eine größere Transferrate sowie eine wirtschaftlichere Zuordnung der Lanes ermöglichen. PCIe 4.0 ermöglicht eine flexiblere Nutzung der Slots und je weniger E/A-Pins belegt werden, desto entsprechend weniger Leistung wird auch verbraucht. Beispielsweise nutzt ein Grafikprozessor (GPU) traditionell 16 Lanes, während ein PCIe 4.0 NVMe-Laufwerk weitere 4 Lanes belegen würde. Die benötigten x4 und x16 Slots können die verfügbaren 20–24 PCIe-Lanes, die auf einem Standard-Mainboard vorhanden sind, schnell ausschöpfen.

Bei PCIe 4.0 hat der Nutzer nun die Möglichkeit, entweder die Bandbreite zu verdoppeln oder die Anzahl der Lanes zu halbieren. Im letzteren Fall könnte er beliebige Plug-Ins mit jeder Kombination von PCIe x4, x8 oder x16 Gerätekarten nutzen.

Darüber hinaus bietet die neue Architektur mehrere Leistungsmerkmale, die die Effizienz erhöhen und den Stromverbrauch senken sollen. Erweiterte Tags und Credits sind Leistungsmerkmale, die die Latenz und Bandbreitennutzung optimieren können. Neu bei PCIe 4.0 sind auch vorteilhafte Funktionen für die Sicherung der Zuverlässigkeit, Verfügbarkeit und Wartungsfreundlichkeit (RAS) zur schnelleren Behebung von Systemfehlern und zur verbesserten E/A-Virtualisierung. Die E/A-Virtualisierung erlaubt, Netzwerkkarten (NIC) oder andere physische Geräte durch virtuelle Softwaregeräte zu ersetzen.

Herausforderungen von PCIe 4.0

Die lange Liste der mit PCIe 4.0 eingeführten Verbesserungen an der Architektur stellt jedoch auch viele technische Herausforderungen. So ist die Einfügedämpfung größer als bei den früheren Generationen. Die Gewährleistung der Signalintegrität bei gleichzeitiger Berücksichtigung der strengeren Margining-Anforderungen stellte die Entwickler vor große Probleme. Aufgrund der höheren Frequenz von PCIe 4.0 verkürzte sich die maximale Leiterbahnlänge von 16–20 Zoll (40,64–50,8 cm) bei PCIe 3.0 auf 10–12 Zoll (25,4–30,48 cm).

Auch hat die größere Bandbreite die an die Leistung des Referenztaktes gestellten Anforderungen entsprechend vergrößert. Jetzt erfordern Entscheidungen zur Takt-Architektur eine gründlichere Analyse, um für Jitter und Frequenz die geforderte Stabilität sicherzustellen. Auch ist zu beachten, dass Taktgeneratoren, die die Anforderungen von PCIe 3.0 erfüllen, nicht notwendigerweise auch ein PCIe-4.0-Gerät unterstützen.

Testanforderungen bei PCIe 4.0

Die größeren Herausforderungen, die das verbesserte Design von PCIe 4.0 stellt, haben auch die Testanforderungen verschärft. Mit der erneuten Verdoppelung der Transferrate werden neue Maßstäbe an die Aufzeichnung, Analyse, Speicherung und Visualisierung der Daten gestellt. Darüber hinaus müssen neue Testplattform-Anwendungen die höhere Frequenz und Kanaldämpfung von PCIe 4.0 berücksichtigen. Das Testen des Referenztaktsignals ist komplizierter geworden, da nun der Phasenjitter aller vier PCIe-Generationen bei allen Datenraten kontrolliert werden muss.

Zu den Hardware-Problemen, die häufiger bei PCIe-Tests festgestellt wurden, gehören Störungen in der Link-Datenrate, in der Signalqualität nach der Wiederherstellung sowie in den Verkehrsströmen. Ein Protokollanalysator ist nicht nur ein vielseitiger PCIe-Tester, sondern auch eine leistungsstarke Lösung zum Überprüfen und Beheben zahlreicher Leistungsmängel in PCIe-Systemen. Angesichts der höheren Transferrate von PCIe 4.0 spielen Funktionen, die es erlauben, mit dem Tester spezifische Datenpakete herauszufiltern und lange Sequenzen aufzuzeichnen, eine immer größere Rolle.

Analyse- und Testlösungen für PCIe 4.0&

Über die gesamte Entstehungsgeschichte des PCIe-Standards hinweg ist die Mess- und Prüftechnik ebenfalls immer weiter entwickelt und angepasst worden, um den Anforderungen gerecht zu werden, die sich aus der jeweils erfolgten Verdoppelung der Transferrate und der wachsenden Komplexität der Architektur ergeben. Zur Gewährleistung präziser und umfassender Tests, sollten daher verschiedene Tools und Prozesse genutzt werden.

Analysatoren, die speziell für PCIe 4.0 entwickelt wurden und tiefgehende Einblicke in die Verkehrsströme sowie eine erweiterte Trace-Analyse ermöglichen, sind unverzichtbar geworden. Testplattformen, wie der Xgig 4K16 Protocol Analyzer/Jammer, stellen zudem eine vorteilhafte Fehlereinfügung zur Verfügung und erlauben, Analyse und Jamming im gleichen kompakten Chassis gleichzeitig auszuführen. Die Segmentierung des Speichers ermöglicht, mehrere Traces aufzuzeichnen. Auch stellt der Speicher von jeweils 64 GB für die Upstream- und Downstream-Richtung mehr als ausreichend Kapazität zur Aufzeichnung der Verkehrsdaten zur Verfügung.

Jammer

Natürlich ist die Jamming-Funktion auch direkt in einen Protollanalysator integrierbar. Separate Geräte, wie der Xgig Jammer von VIAVI, können jedoch Fehler simulieren, indem sie den Live-Verkehr manipulieren, was erlaubt, die Reaktionsgeschwindigkeit und Robustheit der Fehlerbehebungsprozesse zu prüfen. Damit ist es möglich, den Zeitpunkt und den Typ der Fehlereinspeisung exakt zu planen, sodass automatische Testroutinen entwickelt werden können.

PCIe 5.0 und darüber hinaus

Im Mai 2019 wurde die endgültige Spezifikation von PCIe 5.0 verabschiedet. Der Speziellen Interessengruppe PCI ( PCI-SIG) zufolge, die für die Erarbeitung dieser Spezifikationen verantwortlich zeichnet, ist die 5. PCIe-Generation in der Industrie auf ein überwältigend positives Echo gestoßen, was die Entwicklungszyklen für die Hardware und die benötigten Testlösungen beschleunigt hat. Die mit PCIe 5.0 eingeführten elektrischen Verbesserungen haben viele der von PCIe 4.0 her bekannten Probleme mit der Signalintegrität behoben. Natürlich gewährleistet auch diese 5. Generation die uneingeschränkte Abwärtskompatibilität zu den Vorgängerversionen und verdoppelt erneut die Transferrate auf ganz erstaunliche 32,0 GT/s.

Auch wenn PCIe 4.0 ungewöhnlich lange auf sich hat warten lassen, rechtfertigt der große Entwicklungssprung, der mit dieser Version gemacht wurde, diese längere Entwicklungsdauer. Mit der fortlaufenden Übergabe des Staffelstabs erst an PCIe 5.0, dann an PCIe 6.0 und schließlich weiter an die nachfolgenden Technologiegenerationen werden auch die Anforderungen, die an das Design und die Testausführung gestellt werden, immer anspruchsvoller werden. Glücklicherweise hat eine neue Generation von Protokollanalysatoren und anderer vielseitiger Tester eindrucksvoll unter Beweis gestellt, dass sie dieser Herausforderung auch in Zukunft gewachsen sein wird.

Entdecken Sie PCIe 4.0 mit VIAVI!

Sind Sie bereit, mit einem unserer Tester für PCIe 4.0 den nächsten Schritt zu gehen?

Füllen Sie eines der folgenden Formulare aus, um:

Wir stehen Ihnen immer zur Seite

Bei uns erhalten Sie den Support, die Services, die umfassenden Schulungen und die Ressourcen, die Sie benötigen. Diese Leistungen tragen zur Maximierung Ihrer VIAVI Investitionen bei.

Fragen Sie einen Experten

Wenden Sie sich an uns, wenn Sie mehr Informationen oder ein Preisangebot wünschen. Bei uns finden Sie die Experten, die alle Ihre Fragen beantworten können.