PCIe 4.0

業界トップのシグナルインテグリティおよびオートチューニング機能を備えた高度な解析および電波妨害技術

第 4 世代の PCIe は、以前の PCIe 世代との完全な下位互換性を維持しながら、低コストでより広い帯域幅を必要とするアプリケーションに対応しています。

製品

-

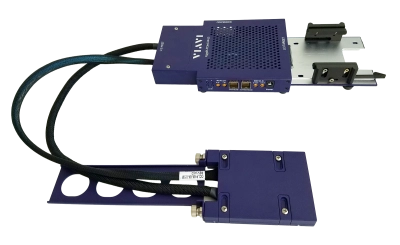

PCI Express 4.0 用 Xgig 4K16 アナライザ / ジャマープラットフォーム

業界最強の PCIe Gen 4.0 解析システムで、高度なトレースと解析機能とジャミング機能によりトラフィックのフローの完全な可視性を提供

-

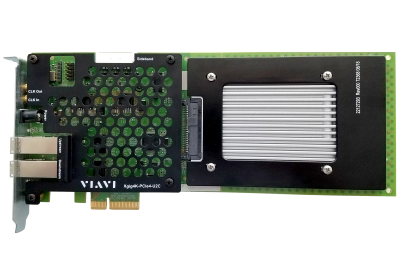

Xgig 4K4 Analyzer Platform for PCI Express 4.0

The Xgig 4K4 platform provides protocol analysis for PCIe and NVMe traffic at all layers of the stack

-

PCI Express 4.0 用の Xgig E1 EDSFF インターポーザー

Xgig4K-PCIe4-X8-E1 は、高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、およびパフォーマンス調整用に最適化されたアクティブインターポーザーです。

-

Xgig CEM Type-B, 16-lane Interposer Module for PCI Express 4.0

The PCIe 4.0 16-lane CEM Type-B Interposer enables debug and verification of new ICs, new system hardware designs,...

-

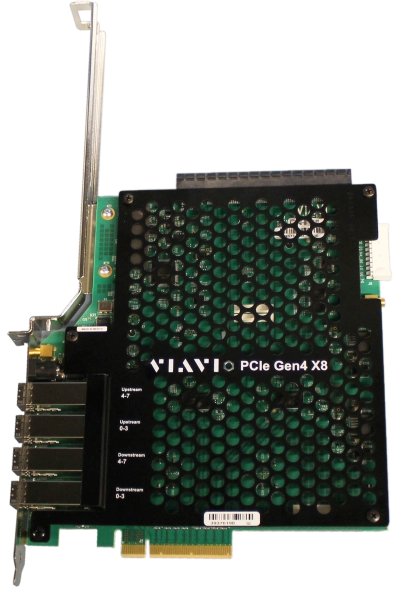

Xgig CEM, 8-lane Interposer Module for PCI Express 4.0

The PCIe4, 8-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA...

-

Xgig CEM-slot, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane CEM-slot Interposer enables debug and verification of new ICs, system hardware designs, FPGA...

-

Xgig U.3 サーバー、PCI Express 4.0 用の 4 レーンインターポーザー

VIAVI PCIe 4.0 アナライザへの入力用にホストシステムと U.3 NVMe SSD 間の通信のタップを提供

-

Xgig U.2 サーバー、PCI Express 4.0 用の 4 レーンインターポーザーモジュール

この U.2 サーバー、バージョン B インターポーザーは、高密度ストレージサーバーでの NVMe SSD 動作の開発、デバッグ、およびチューニング用に最適化されています。

-

Xgig U.2-CEM, 4-lane Interposer Module for PCI Express 4.0

This U.2-CEM Interposer is optimized for NVMe SSD development enabling debug and analysis

-

Xgig M.2、PCI Express 4.0 用の 4 レーンインターポーザーモジュール

PCI Express® 4.0 用の M.2、4 レーンインターポーザーは、M.2 SSD 開発用に最適化設計されたアクティブインターポーザーです。

-

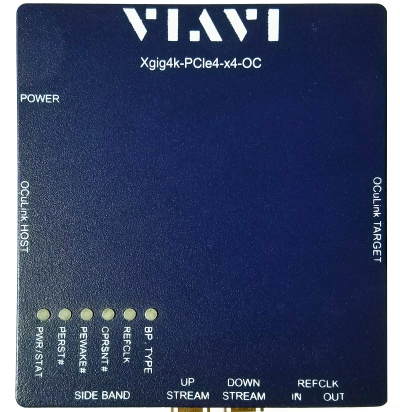

Xgig Oculink, 4-lane Interposer Module for PCI Express 4.0

The PCIe4, 4-lane OCulink/Slimline Interposer enables debug of new ICs, hardware designs, FPGA firmware, system BIOS...

-

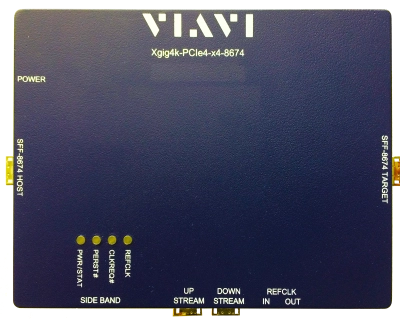

Xgig SFF-8674, 4-lane Interposer Module for PCI Express 4.0

The SFF-8674 Interposer enables protocol analysis of PCI Express 4.0 traffic between an SFF-8674 attached host...

-

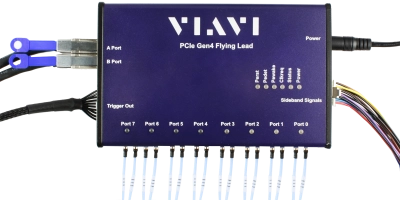

Xgig Flying-Lead, 4-lane Interposer Module for PCI Express 4.0

The Xgig Flying-Lead Interposer captures signals between controller ICs on the same PCB where there is no connector...

-

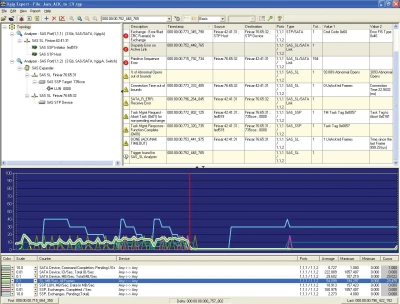

Xgig Expert

すべての Xgig アナライザには Expert ソフトウェアが標準装備されており、デバイス開発とトラブルシューティングを高速化し簡素化するように特別に設計された、デバッグおよび分析機能の独自で堅牢なセットを提供します。

-

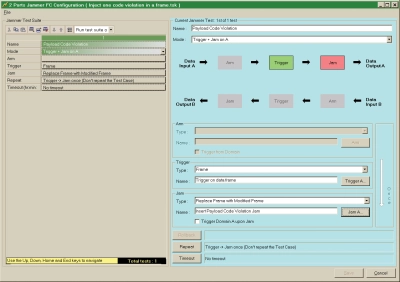

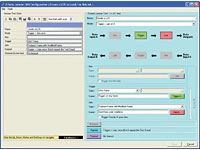

Xgig ジャマー

Xgig® ジャマーはライブネットワークトラフィックを操作することで、エラーをリアルタイムでシミュレートし、エラー回復プロセスの応答性と安定性を検証できるようにします。

-

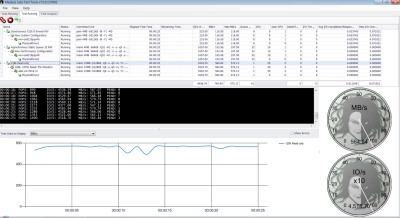

Medusa Labs テストツールスイート

Madusa Labs テストツールスイート(MLTT)は、アプリケーションベースのデータおよびシグナルインテグリティのテストツールで、開発者が製品を市場にリリースする前にストレステストを通して見つけにくいエラーを特定し、見つけ、...

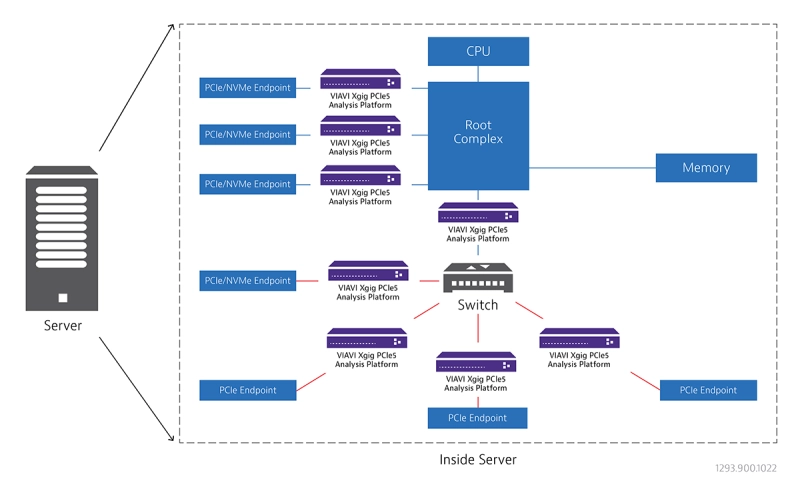

x1 x2、x4、x8、x16、x32 などの可変レーンレートとレーン幅により、開発者は柔軟なパフォーマンスレベルにアクセスでき、システム帯域幅とパフォーマンス構成に応じてアプリケーション要件を最適化することができます。Xgig PCIe 4.0 プラットフォームは、4K4 4 レーンのアナライザシャーシと、アナライザとジャマー機能を備えた 4K16 16 レーンシャーシで構成されています。この製品ラインには、PCIe4 インターポーザーの完全なセットも含まれています。VIAVI は、PCIe 5.0 用の Xgig Exerciser を使用する PCI-SIG コンプライアンスワークショップで実施される PCI Express (PCIe) 4.0 プロトコル適合認定試験に関して認定を受けた試験装置ベンダーです。

PCIe 4.0 とは

x1 x2、x4、x8、x16、x32 などの可変レーンレートとレーン幅により、開発者は柔軟なパフォーマンスレベルにアクセスでき、システム帯域幅とパフォーマンス構成に応じてアプリケーション要件を最適化することができます。Xgig PCIe 4.0 プラットフォームは、4K4 4 レーンのアナライザシャーシと、アナライザとジャマー機能を備えた 4K16 16 レーンシャーシで構成されています。この製品ラインには、PCIe4 インターポーザーの完全なセットも含まれています。VIAVIは、PCIe 5.0 用の Xgig Exerciser を使用する PCI-SIG コンプライアンスワークショップで実施される PCI Express (PCIe) 4.0 プロトコル適合認定試験に関して認定を受けた試験装置ベンダーです。PCIe 4.0(PCIe 4、PCIe Gen 4、PCI 4、PCI Express 4.0 とも呼ばれる)は、高速コンピュータバステクノロジーである Peripheral Component Interconnect Express (PCIe) の第 4 世代です。AMD、ゲーム、Flash コンテンツなど、低コストでより広い帯域幅を必要とするアプリケーションに対応する設計になっており、また「PCIe 4.0 の下位互換性」について言えば、PCLe 4 は前世代の PCIe と完全な下位互換性を維持しています。

この仕様では、可変レーン幅(x1、x2、x4、x8、x16、x32)が定義されています。これにより、開発者は多数のレーン幅と速度設定にアクセスでき、さまざまな帯域幅要件を持つアプリケーションに対応できます。例えば、ストレージアプリケーションは PCIe x4 レーン幅を使用しますが、 帯域幅の増加によってメリットを得られる高性能アプリケーションは PCIe x16 レーン幅を使用できます。

互換性のある PCI Express 4.0 マザーボードと PCI gen 4 SSD を組みあわせると、前世代の PCIe 3.0 シリーズ の SSD の 2 倍のシーケンシャル読み取り/書き込み速度が達成され、より低速な SATA SSD テクノロジーの 10 倍以上の速度が達成されます。

PCI Express 4.0 の仕様は 2017 年 10 月に、その前のバージョンの PCIe 3.0 の 2 倍のビットレートである 16GT/秒の公表転送(ビット)レートで確定されました。下の表に、PCIe 3.0 と PCIe 4.0 が提供する集約帯域幅のオプションを示します。

| GBPS 単位の帯域幅 | PCIE X1 | PCIE X2 | PCIE X4 | PCIE X8 | PCIE X16 |

|---|---|---|---|---|---|

| PCIe 3.0 | 1.97 | 3.94 | 7.87 | 15.75 | 31.51 |

| PCIe 4.0 | 3.94 | 7.87 | 15.75 | 31.51 | 63.02 |

PCIe 4.0 の違い

2003 年には、PCI Express の第 1 世代である PCIe 1.0 がリリースされ、ほぼ同時にその直前のバス規格である PCI および AGP(アクセラレーテッドグラフィックスポート)に取って代わりました。後者は、より広い帯域幅を必要とするグラフィックスコントローラー接続用に特に開発されました。

PCI の改良点は、PCI のパラレル形式に代わるシリアルインターフェイスフォーマットと、ぎくしゃくした PCI 共有バスアーキテクチャーに代わる接続された各デバイス用の個別のバスにより、容易に明らかになるものでした。PCIe 1.0 (当初は高速インターコネクトと呼ばれていました)は、1 レーンあたり 250MB/秒の帯域幅仕様と 2.5GT/秒 の転送レートを誇っていました。

PCIe のフルリリースごとに帯域幅を倍増させるという取り決めは、それぞれ 2007 年と 2010 年にリリースされたバージョン 2.0 と 3.0 で確立されました。PCIe 3.0 の増分改善には、8b/10b から 128b/130b に更新されたエンコーディング方式が含まれています。PCIe スロットと接続カードの間の最小バージョンと速度は、常に実際の帯域幅のパフォーマンスと時間の制約を左右しますが、連続した反復ごとに、PCIe は以前のバージョンと下位互換性が維持されています。

PCI Express 4.0 の最終リリース仕様は、それまでの 4 年ごとのリリースから逸脱し、PCIe 3.0 から丸 7 年後まで延長されました。後方互換性のある機械的および電気的なフォームファクターにより、帯域幅倍増のために確立された PCIe 規格を維持 することは、開発者にとってより困難な作業であることが実証されています。

PCIe Gen4 では、この困難な性能の期待に応える一方で、システムレイテンシの削減、帯域幅の追加レーンのための拡張性、PCIe チャネルの各レーンの電気的整合性と信頼性を評価するレーンマージン機能などの機能向上も導入されました。

PCIe Gen4 の速度

非常に多くの改良が加えられましたが、PCIe 4.0 の速度の大幅な向上は最も重要な改良点であり続けており、これを土台に、新しいアプリケーションのための数多くの利点と手段が生まれてきました。連続するリリースごとに速度が向上したため、PCIe x4 (4 レーン)は、第 1 世代の PCIe x16 (16 レーン)のスループットを上回るレベルになりました。

現実的なコンテキストを提供すると、PCI Express 4.0 規格の転送レートは、1 秒あたり 1600 万回発生する差動ペアの電圧切り替えを示しています。

この PCIe * の速度倍増の伝統により、クラウドサーバーやデータセンターなどのハイエンドアプリケーションで PCIe * 4.0 のコスト削減が可能になり、ノートブック PC やタブレットなどのスタンドアロンデバイスのパフォーマンス、ユーザー体験、不動産効率が向上しました。

過去 16 年間でビットレートと帯域幅の仕様が劇的に増加しているにもかかわらず、ネットワークアーキテクチャの不可欠な要素に対応するためには、さらに高速化が必要になります。400G イーサネットテクノロジーは、PCI Express Gen4 の最大速度を超えてペースを維持するために、各方向に 50GB を必要とします。x86 アーキテクチャではバスが多くの場合、ボトルネックとなることがあるため、高度なアプリケーションは、将来の世代の PCIe で約束される優れた帯域幅をすでに待っている可能性があります。

| バージョン | 転送レート | スループット/レーン | x16 スループット |

|---|---|---|---|

| PCIe 1.0 | 2.5GT/秒 | 250MB/秒 | 4.0GB/秒 |

| PCIe 2.0 | 5.0GT/秒 | 500MB/秒 | 8.0GB/秒 |

| PCIe 3.0 | 8.0GT/秒 | 1.0GB/秒 | 16.0GB/秒 |

| PCIe 4.0 | 16.0GT/秒 | 2.0GB/秒 | 32.0GB/秒 |

PCIe 4.0 のアーキテクチャ

PCIe 4.0 のアーキテクチャは、速度の向上とより経済的なレーン割り当てを提供することを目的としています。PCIe Gen4 によって可能となる I/O ピンの使用量が減少すると、消費電力が比例的に改善されます。例えば、GPU は従来 16 レーンを使用していましたが、PCIe 4.0 NVMe ドライブはさらに 4 レーンを消費します。この PCIe x4 と x16 の要件により、標準的なマザーボードに搭載されている 20~24 PCIe レーンをすぐに使い果たされる可能性があります。

PCIe Gen4 の登場により、ユーザーは帯域幅を 2 倍にするかレーンを半分にするかを選択できるようになりました。後者は、PCIe x4、x8、または x16 デバイスカードの任意の組み合わせを使用して、より任意のプラグインを提供する機会を提供します。

PCI Express Gen4 アーキテクチャには、効率と消費電力を向上させるためのいくつかの追加機能も含まれています。サービスデバイスの拡張タグおよびクレジットは、レイテンシをマスクし、帯域幅の飽和を最適化できる機能です。システムエラーを拡大し、I/O の仮想化を改善する優れた信頼性、可用性、および保守性(RAS)機能は、PCIe 4.0 の他の新要素の 1 つです。I/O 仮想化を利用することで、仮想ソフトウェアデバイスにより、ネットワークインターフェイスカード(NIC)などの物理的に同等なデバイスを置き換えることができます。

PCI Express 4.0 の課題

PCIe 4.0 に組み込まれた数多くのアーキテクチャの改良点は、多くの技術的課題ももたらしています。挿入損失が以前の改訂版で発生した値よりも大きくなっています。より厳しいマージニング要件に適応しながらシグナルインテグリティを維持することは、克服すべき大変困難な障害となっています。PCIe Gen4 に伴う周波数が高いため、最大トレース長は PCIe Gen3 で 16~20 インチから 10~12 インチになりました。

最近の帯域幅の増加はまた、基準クロックのパフォーマンス要件も比例的に増加させています。適切なクロッキングアーキテクチャの決定には、十分に低いジッターと周波数の安定性レベルを確保するために、より多くの分析が必要になります。また、PCIe 3.0 の要件を満たすクロックは、必ずしも PCIe 4.0 デバイスのニーズを満たしているとは限りません。

PCIe 4.0 のテスト

PCIe 4.0 の設計拡張に固有の課題も、テストの領域にまで広がっています。PCIe 4.0 の速度がさらに倍増したことで、データのキャプチャ、分析、保存、可視化のためのより高い標準が生まれました。PCIe Gen4 に固有の高い周波数とチャネル損失は、新しいテストプラットフォームアプリケーションの追加の考慮事項です。リファレンスクロックのテストは、4 つの PCIe イテレーションとデータレートすべての位相ジッター要件テストが必要になるため、より複雑になっています。

PCIe テスト中に見られる一般的なハードウェアの問題には、リンク速度の問題、トラフィックの問題、復元後のリンク品質の問題などがあります。プロトコルアナライザは、汎用性の高い PCI Express テスターであり、多くの PCIe の問題をテストおよびデバッグするための強力なソリューションです。PCIe 4.0 の高速化により、特定のパケットをフィルタリングし、長いシーケンスを記録する機能は、ますます価値のあるテストデバイス機能となっています。

分析およびテスト用ソリューション

PCIe 規格の歴史を通じて、PCIe 帯域幅テスト装置は、速度の増加やアーキテクチャ内の複雑さの増大に対する要求を満たすために進化し、適応してきました。正確かつ包括的なテストを確実に行うためには、複数のツールとプロセスを使用する必要があります。

プロトコルアナライザ

PCI Express 4.0 専用に設計されたアナライザは、トラフィックフローに対する高レベルの可視性と高度なトレース解析機能を備えており、不可欠になっています。Xgig 4K16 プロトコルアナライザ/ジャマーなどのテストプラットフォームは、エラー注入機能の利点と、単一のシャーシで同時に分析およびジャムを行う手段も提供します。メモリセグメンテーションは、複数のトレース内容のキャプチャを可能にします。上り回線と下り回線の両方に 64GB のメモリーを搭載しているため、トラフィックデータのキャプチャ用のストレージ容量も十分です。

ジャマ―

ジャミング機能はプロトコルアナライザに統合されている機能ですが、Xgig ジャマーなどの個別製品では、ライブトラフィックを操作してエラーをシミュレートできるため、エラー回復プロセスの応答性と堅牢性を検証することができます。自動 PCIe 速度テストルーチンを開発できるように、導入するエラーのタイミングや種類を事前に正確に計画することができます。

PCIe 5.0 以降

PCIe 5.0 仕様の最終リリースは 2019 年 5 月に完成しました。PCIe リリースを担当するグループ PCI-SIG によれば、PCIe 5.0 は業界から積極的な反応を集めており、ハードウェアおよびテストソリューションの開発サイクルの高速化につながっています。PCIe 5.0 固有の電気的改善は、PCIe Gen4 で観察される多くのシグナルインテグリティ問題に対応しています。慣例に従い、PCIe Gen 5 は、完全な下位互換性と PCI Express 4.0 の 2 倍、すなわち驚異的な 32.0GT/秒の PCIe 転送レートを提供します。

PCIe 4.0 の登場には通常よりも非常に時間がかかりましたが、これらの飛躍的前進のおかげでその辛抱も報われたと言ってよいでしょう。PCIe 5.0、PCIe 6.0 へと次々にバトンを引き渡すことで、設計およびテストの専門家に対する要求は衰えることなく継続されます。幸いなことに、新しい世代のプロトコルアナライザやその他の汎用テスターは、この課題に値することが証明されており、将来の世代にも十分に対応できるようになっています。

VIAVI の PCIe 4.0 を今すぐご確認ください。

VIAVI の PCIe 4.0 テスターで次の一歩を踏み出す準備ができていますか?

以下のフォームの 1 つに記入して、始めましょう。

あらゆるステップでのサポート

VIAVIは、サポート、サービス、総合的なトレーニング、お客様が必要とするリソースを提供しています。これはすべて、お客様のVIAVIへの投資価値を最大化するために当社が日頃より行っていることです。

エキスパートに尋ねる

詳細、価格のお見積りについてお問い合わせください。Viaviのエキスパートがお客様のあらゆる質問にお答えします。