PCle テスト機器

PCIe スタックのすべてのレイヤーでの通信の詳細な解析

PCIe(Peripheral Component Interconnect Express)は、プロセッサを周辺機器、メモリー、およびその他のコンポーネントに接続するために使用される業界標準の高速コンピュータバスアーキテクチャです。現在第 6 世代となっている PCIe は、ポイントツーポイントトポロジーを使用して、接続されている各デバイスへ個別のリンクを提供します。

PCIe が継続的に反復を繰り返すたびに速度と帯域幅が倍増し、データのキャプチャ、ストレージ、および視覚化プロセスが複雑になるにつれて、PCIe のテストプロセスはより困難になっています。2003 年の 第一世代の PCIe のリリース以降、PCIe テストツールはこれらの課題に対処するために継続的に適応および改善されてきました。今日では、PCIe テスト機器一式を利用して、正確で効率的な PCI Express のトラブルシューティングとテストを行うことができます。

Peripheral Component Interconnect Express ガイド

一般に PCI Express および PCIe という頭字語で知られる Peripheral Component Interconnect Express は、ほぼすべての内部コンピュータコンポーネント接続の業界標準となっている高速コンピュータバスアーキテクチャです。

PCIe はコンピュータのプロセッサとメモリーからその他のコンポーネントと周辺機器への接続を提供します。このインターフェイスは、PCI および ISA(Industry Standard Architecture)を含む古いパラレルバスアーキテクチャを置き換えるために設計された高速シリアルトランスポートです。PCIe は、従来のものに比べデータ転送速度が著しく改善されたポイントツーポイントアクセスバスを使用します。

1980 年代の早期のコンピュータバス アーキテクチャは CPU と全コンポーネント間のパラレルデータパスに基づいていました。

1990 年代の後期には、PCIe の前身が開発され、マザーボードの対応位置にスライドさせて装着した接続デバイスカードのお馴染みのフォームファクターを統合しました。PCI バスには 32 ビットと 64 ビットのバージョンがあり、一方で AGP(アクセラレーテッド グラフィックス ポート)が PCI バスで提供できるより広い帯域幅のグラフィックコントローラ接続用に特別に開発されました。今日では、両インターフェイス共、ほとんどが PCI Express で置き換えられています。

2000 年初期までには、内部ハードウェアおよび周辺機器による処理帯域幅に対する需要増により PCI Express または PCIe として知られる次世代 PCI へ移行するに至りました。従来型 PCI に比較した PCIe の最大の利点は、PCI アーキテクチャで使用されていたパラレルインターフェイスではなく シリアルインターフェイスを使用することです。もう一つの利点は、接続された機器が共有バスではなくそれぞれ個別のバスを使用する点です。

データ転送性能は、必要接続機器での複数レーンの使用によりさらに向上しています。割り当てられている接続データポート数で定義されるレーンの増加、つまり x1(1 倍)から x16(16 倍)は、対応するデータ転送量の増加を表します。これで、容量が必要とする場合、ポイント A からポイント B に移動するデータは複数のバスにて同時に運ぶことができるようになります。

事実上の標準として PCIe は広く受け入れられて人気を博し、USB、Bluetooth、ビデオカードを含む、さまざまな機能コンポーネントがこのプラットホームを採用することになりました。ビデオコントローラやストレージデバイスは、PCIe アーキテクチャの出現で実現されたテクノロジーの一例です。 これは、過去 10 年間に経験したグラフィックスとコンピュータの性能の改善が何よりの証拠です。

PCI Express バージョンのアーテクチャに含まれるブレークスルーにより、PCI と比較して転送速度が大幅に高速になり、その後の各バージョンはこれらの改善の上に構築され続けています。従来の PCI は、共通のアドレス、データおよび制御ラインを利用していましたが、PCIe のポイントツーポイントトポロジーは、接続された各デバイスに別々のリンクを提供し、他のデバイスの潜在的な制約からそれぞれを解放します。

PCIe による通信では、「パケット」と呼ばれるデータ転送モードを使用します。PCIe ポートのトランザクションレイヤーは、データのパケット化とパケット解除の作業を行います。PCIe と従来式 PCI の電気信号方式の違いにより、異なる電気およびコネクター アーキテクチャの開発が必要で、PCIe スロットが PCI カードと非互換になりました。

PCI Express 用に各種のフォーマットが開発されており、それぞれわずかに異なる命名方法を使用しています。これらの PCIe フォーマットがサイズとバージョンに関して何を示しているのかを学ぶことが重要です。これらは、どの拡張カードがシステムで動作するか(または動作しないか)を理解するために重要なリソースです。

PCI Express のバージョン

2002 年に PCIe 1.0 が発表されて以来、帯域幅と速度に対する増加する需要を満たすために連続してリリースが行われてきました。バージョン 1.0 では、合計 16 レーンのトラフィックで 8 GB/秒未満の帯域幅を使用できましたが、PCIe 1.0 の転送レートは 2.5 ギガトランスファー毎秒(GT/s)でした。新しいリリースごとに帯域幅の合計が 2 倍になり、最終的には 2019 年にリリースされた PCIe 5.0 の帯域幅は 128 GB/秒になりました。同時に、転送レートは 2.5 GT/s から 32.0 GT/s に段階的に上昇してきました。性能の改善に伴い、各バージョンは新機能を提供し、エネルギー効率も向上してきました。

2~3 年ごとに帯域幅を倍増してプロセッサー速度とメモリーの急増に追いつき、ボトルネックになることを避けるという厳しい基準を満たすために、各バージョンは設計者に新しい課題を投げかけます。帯域幅の増加に沿ってクロストークと電気的な不連続性が増えるため、新素材とデザインの革新により限界に挑んでいます。

PCIe のサイズ

PCI Express カードのサイズとピン数は、レーン数と合計接続数によって決まります。これはすべての PCIe バージョンで同様です。利用可能なサイズとそれに対応するピン数は以下の通りです。

| タイプ | 長さ | ピン数 |

| PCI Express x1 | 25mm | 18 ピン |

| PCI Express x4 | 39mm | 32 ピン |

| PCI Express x8 | 56mm | 49 ピン |

| PCI Express x16 | 89mm | 82 ピン |

PCI カードとは異なり、スロットがカードと同じサイズかそれより大きい限り PCI Express カードはどのサイズの PCIe スロットにも装着できます。これは、x1 拡張カードは x1、x4、x8、または x16 スロットに装着できることを意味します。この逆も適応可能で、x16 カードは x4 スロットに装着できますが、これができるのはそのスロットの背後が開いたタイプの構成である場合のみです。ただし、この場合には帯域幅は x4 カードの帯域幅に限定されます。

PCIe カードで利用可能な帯域幅は、CPU またはマザーボード PCIe コントローラの改訂によっても左右され、コントローラがバージョン 4.0 用に構成されている場合、バージョン 5.0 カードはバージョン 4.0 カードの帯域幅でしか動作しないことを意味します。

最初の PCIe 1.0 は 8GB/秒の帯域幅しかありませんでしたが、バージョンごとに速度は倍増し、PCI Express 5.0 では、16 レーンのトラフィックで 128GB/秒にまで至りました。帯域幅が増加するにつれて、クロストークや不連続性の可能性も高まり、PCB トレース材料やレーンマージンにおける最近のイノベーションがこの急速な進化の必要条件となっています。PCI Express フォーマットの技術的汎用性は、もう 1 つの重要な要素であり、互換性に重点を置くことで、PCIe テスト機器とハードウェアの設計者に等しく影響を与えてきました。改訂版間の下位互換性は引き続き顕著な特徴であり、1x~16x のスロットサイズは、どのサイズの PCIe カードにも適合し、2 つの項目のうち小さい方が帯域幅の可用性を決定します。

PCIe と NVMe

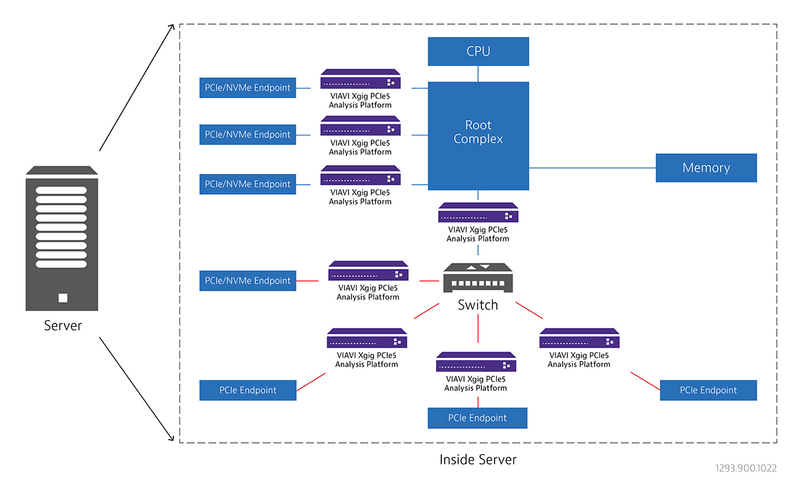

不揮発性メモリエクスプレス(NVMe)は、PCI Express で使用するために特別に開発されたソリッドステートドライブ(SSD)メモリープロトコルです。この文脈での「不揮発性」とは、データを保持するために電力を必要としないメモリーを指します。NVMe は PCIe * アーキテクチャの利点を活用して、12 Gbps SAS インターフェイスの 2 倍以上の読み取り/書き込み速度を実現しています。NVMe は、従来の I/O コントローラーを使用する代わりに、PCI Express を介して CPU への直接接続を利用します。PCIe/NVMe の組み合わせを効果的にテストするには、ハイエンドのメモリー容量とセグメンテーション機能を備えた PCIe テスト機器が、正確な NVMe トラフィックのデコードに不可欠です。

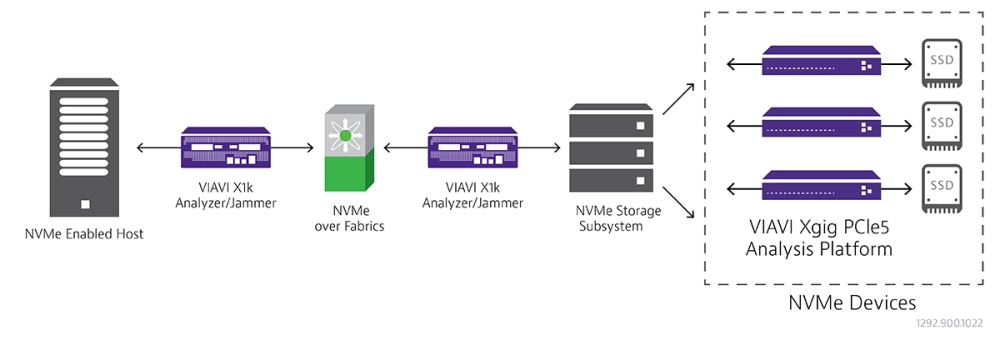

NVMe over Fabrics (NVMe-oF)の使用により、NVMe ストレージデバイスとホストの間の範囲を拡大することになるため PCIe テストに課題が加わりますが、10µs 以下の追加レイテンシー導入目標は維持しています。NVMe-oF の仕様は本質的に NVMe の基本仕様と似ていますが、転送メカニズムの特性評価はさらに複雑になります。回路の NVMe 対応ホストと NVMe デバイスの両端で適切な PCIe/イーサネット/ファイバーチャネルアナライザ/ジャマーテスト機器を使用することが推奨されるベストプラクティスです。

PCI Express 4.0

2017 年 10 月にリリースされた PCI Express 4.0 では、新しい世代ごとに固有の従来から行われてきた速度と帯域幅の向上ととも、レーンマージンやレイテンシの削減などの改善がもたらされました。拡張タグとクレジット、および拡張 I/O 仮想化は、PCIe 4.0 リリースに追加された拡張機能であり、その後の各世代で引き続き最適化されます。第 4 世代の PCIe の採用により、速度の向上とその結果発生する挿入損失およびマージンの要件によってもたらされる PCI Express テストの課題の多くに対する可視性が向上しました。トラフィックフローの監視、データストレージ、およびエラー検出機能には、PCI Express ツールのより高いパフォーマンス標準が必要であり、この傾向は PCIe 5.0 以降でも衰えることなく続いています。

PCI Express 5.0

2019 年 5 月の PCIe 5.0 のリリースでは、新しい機能やアーキテクチャの大幅な変更を最小限に抑えながら、必要な 2 倍の速度と帯域幅の向上を達成することに重点を置いた開発サイクルが加速されました。第 5 世代の PCIe は、第 4 世代の 128b/130b エンコーディング方式、NRZ シグナリング、およびジッターパラメータを継承されています。2 倍の速度向上を補完するために、電気的デザインはシグナルインテグリティとイコライゼーションに重点が置かれました。結果として得られる I/O スループットとパフォーマンスの組み合わせにより、第 5 世代の PCIe は、400G イーサネットリンクや要求の厳しいクラウドベースのネットワーキングの実行可能な選択肢となりました。

PCIe テスト機器の貴重な可能性

第 1 世代の PCIe のリリース以来、効果的な PCI Express テストの課題は、さまざまな種類の PCIe テスト機器とソフトウェアの開発により対処されてきました。これらのツールは、パフォーマンスを正確に測定し、問題を迅速に検出し、使用条件をシミュレートして堅牢かつ包括的な分析を行うように設計されています。新しい革新的なプロトコル/ジャマーの組み合わせは、NVMe-oF などの複雑な使用条件に最適であることが実証されています。

トラフィックフローとリンクパフォーマンスを詳細に可視化するアナライザにより、転送速度とメモリーの急増するテストソリューション要件をサポートしつつ、PCIe 5.0 プロトコルの包括的な検証が可能となっています。ライブトラフィックを操作する機能を備えたジャミングツールは、他の方法では不可能な強固なシミュレーションを実現します。これらの最先端の PCIe ツールの背後にあるソフトウェアは、オペレータを PCI Express テストケースにシームレスに結びつける、改善し続けるインターフェイスとレポート機能の強化により、すべてを結び付け続けています。

PCI 専門部会(PCI-SIG)は、PCI Express システムの相互運用性を保証するために必要な仕様とコンプライアンステストを定義しています。同部会は、1992 年に設立され、現在では PCI-SIG が発表した仕様に基づいて製品を開発する 800 社以上の会員企業が参加しています。これらの仕様は、メンバーの組織または個人が自由に使用できます。PCI-SIG はまた、PCIe テスト、技術サポート、およびコンプライアンスに関するワークショップも提供しています。PCI-SIG 準拠ライブラリには、推奨される機器の包括的なリストが含まれています。

PCI-SIG 仕様に含まれている PCI Express テストのカテゴリには、電気的テスト、設定テスト、リンクプロトコルテスト、トランザクションプロトコルテスト、プラットフォーム BIOS テストなどがあります。チャネルトポロジは、データレートの増加に伴い、はるかに複雑になっています。シミュレーションを使用して電力とシグナルインテグリティを最適化することは、PCIe のリンク評価の推奨される方法です。データパケットが確実に転送されるかどうかは、物理レイヤーでプロトコル検証を使用して判断できます。トランザクションプロトコルテストは、望ましくないエラーをチェックしてデバッグし、PCI-SIG へのコンプライアンスを保証します。

さまざまな PCIe テストツールが利用できるようになりました。PCI Express テスト機器は、世代を重ねるたびに厳格になる要求に応えるべく進化し、新しくエキサイティングなソリューションを実現してきました。業界トップの PCI Express テスト機器サプライヤが提供する機能豊富なツールは、理想的なモバイル性と堅牢性を備え、トレーニングと認証試験もすぐに利用することができます。インターフェイスには下位互換性があるため、複数のサイズとバージョンの相互運用性と迅速なアップグレード性が、卓越した PCIe テスト機器のその他の全体的な特徴となっています。

ジャマー

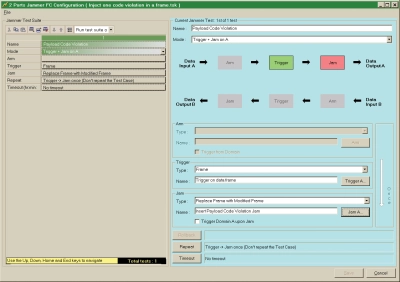

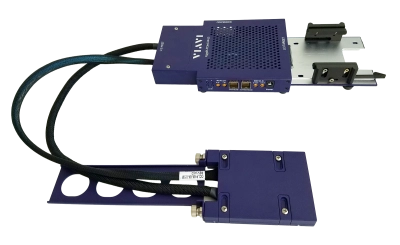

ジャマーを使うことで、ライブトラフィックを操作して、リアルタイムでエラーをシミュレートできます。「ジャミング」という用語は、敵のデジタル通信回線を妨害するために導入された意図的な干渉を表すために、20 世紀初頭に生まれました。PCIe テストでは、ジャマーはインラインエラー注入ツールで、実際の状態をシミュレートし、テストサイクルを短縮できます。多くの場合、あらかじめ定義された自動テストスクリプトを使用して、ジャマーはさまざまなエラーテストシナリオを再現できます。

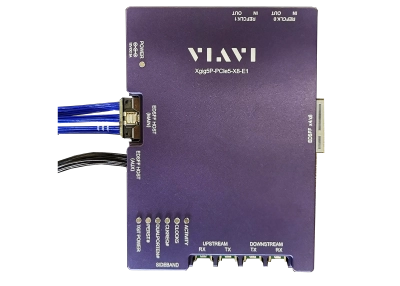

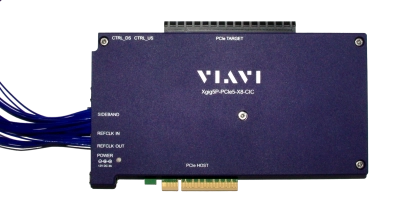

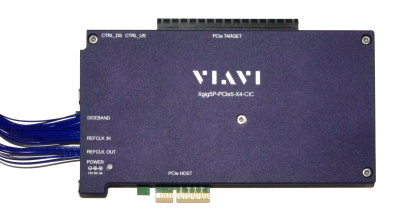

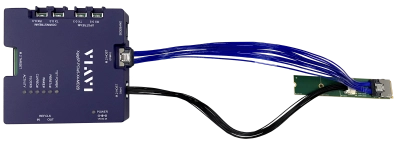

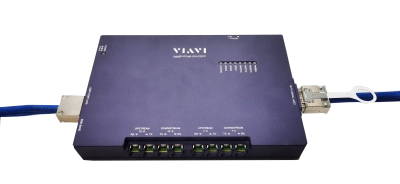

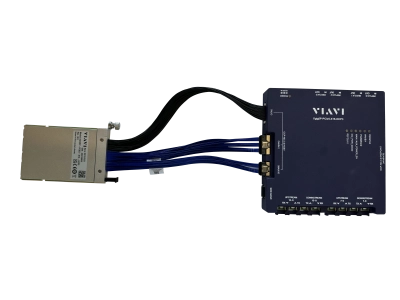

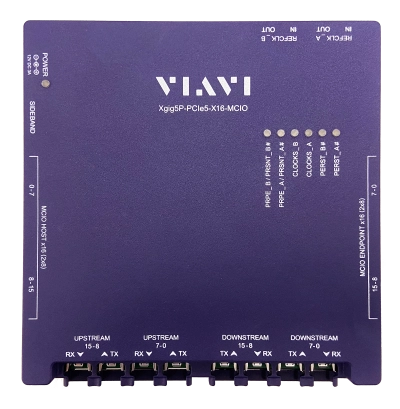

Xgig などのジャマーは、高度にインテリジェントでプロトコルに対応しており、条件付きジャミングを利用してテストプロセスを制御し、包括的なテスト範囲を確保できます。プロトコルアナライザやその他の PCIe テスターと連携して、ジャマーはエラー注入ポイントで識別可能なトリガーを生成します。実際の環境にエラーを導入することで、エラー復旧プロセスの応答性と有効性を正確に見定めることができます。

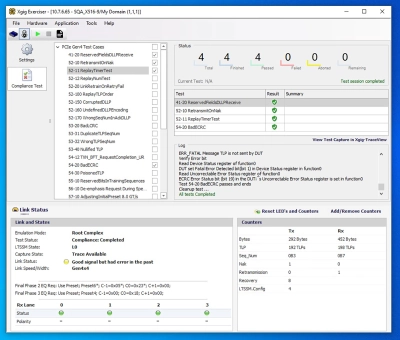

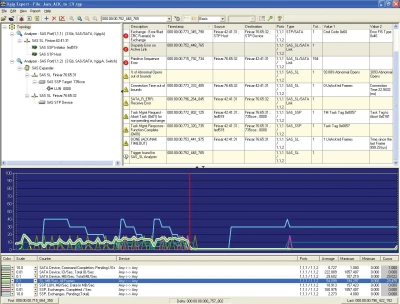

アナライザ

プロトコルアナライザは、バススループットとリンクパフォーマンスの測定、およびパケットの監視と記録を行うための多目的な PCI Express 製品ツールです。追加のトリガー、エラーレポート、およびフィルタリング機能により、迅速なエラー識別が可能になります。ジャミング機能は、エラー検出機能を実行するための遅延や再送信を人為的に生成することができます。

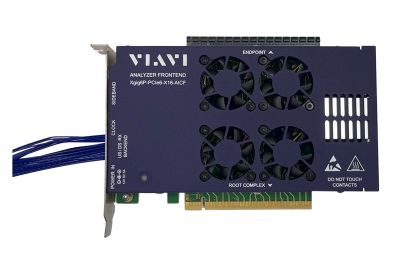

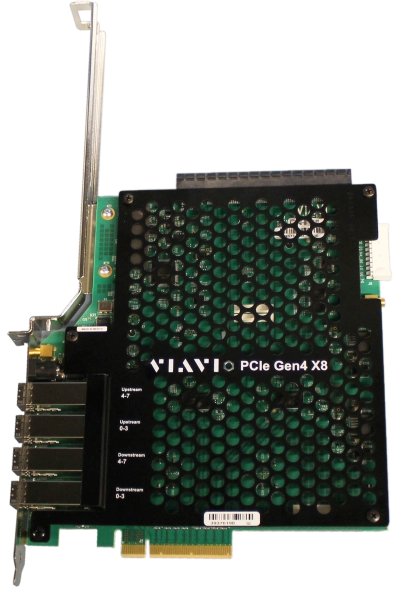

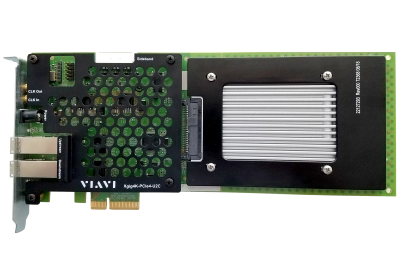

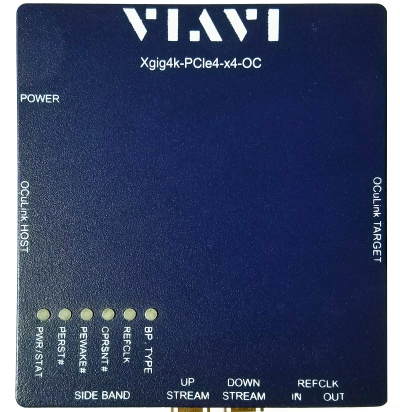

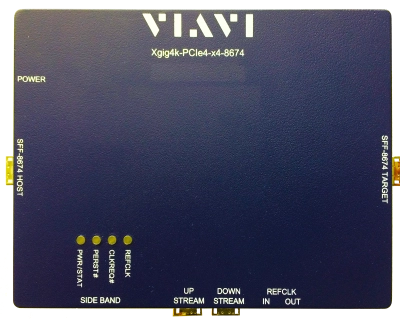

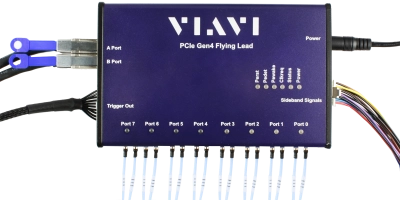

高度なトレース分析、トラフィックフローの可視化、メモリーセグメンテーション機能を備えた強力なアナライザは、非常に貴重です。Xgig 4K16 プロトコルアナライザ/ジャマー を使用すると、エラー注入とプロトコル分析を同時に実行できます。相互運用性機能には、x1、x2、x4、x8、x16 のレーン幅サポートが含まれます。スタックの各レイヤでエラーが発生した場合にユーザーにアラートが送信され、高度なメモリー使用率により、複数のトレースを同時にキャプチャできます。

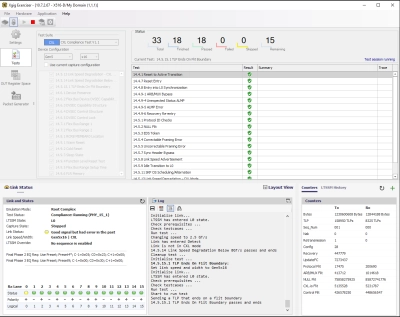

ソフトウェア

PCIe テストソフトウェアは、プロトコルアナライザとジャマーテクノロジーが、速度、機能性、および汎用性の要件の増加に対応し続けてきた元になるバックボーンです。適切に設計されたソフトウェアは、反復的な機能を自動化し、リリースされた仕様に基づいてカスタマイズされたルーチンを作成し、複数のツールを統合してシームレスな機能を実現するのに役立ちます。高度なレポーティングソフトウェアにより、複雑なデータ分析を簡素化し、最適な解釈を容易に実行できます。

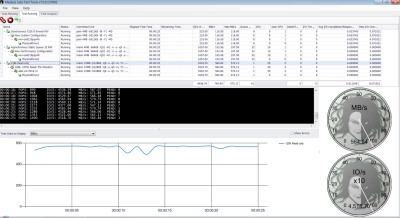

すべての Xgig アナライザに付属の Xgig Expert ソフトウェアは、データの迅速な解釈、デバッグ、およびトラブルシューティングに役立つ使いやすいインターフェイスを生成します。このソフトウェアは、キャプチャされたイベントを効率的に分類して、パフォーマンスと相互運用性の問題の特徴を明らかにし、プロトコル違反を含む物理層の問題を特定し、オンデマンドで結果を包括的なレポートにまとめます。追加のレポート作成ソフトウェアを使用すると、効率的なデータ管理のフィルタリング、分析、プレゼンテーション機能を可能になります。

PCI Express の不具合のトラブルシューティングは、しばしば困難な作業になることがあります。幸いなことに、すぐに利用できる多くの PCIe ツールは、優れたデバッグ機能とトラブルシューティング機能も備えています。効果的な PCIe テストとトラブルシューティングの鍵となるものには、トラフィックフローの可視性の向上や、最も多く見られるハードウェアの問題に対する知見などがあります。これらの問題には、イコライゼーションの障害、トラフィックの問題、回復後に確認される品質の問題など、リンク速度の問題が含まれます。エラーレポートソフトウェアは、アプリケーション固有のエラーを検出してログに記録し、タイムアウトやデータ転送の停止などのエラータイプを特徴づけることができます。

分析ソフトウェアを搭載したプロトコルアナライザは、重要で効果的な PCIe トラブルシューティングツールになる可能性があります。アナライザを使用すると、問題と発生順序を特定するために必要なトラフィックフローと履歴データを簡単に確認できます。また、アナライザには強力なトリガー条件があり、非常に長いシーケンスをキャプチャし、特定のパケットをフィルタリングする機能により、調査能力をさらに高めることができます。時間順シーケンスのロギングは、レポートされたエラーの前後にイベントを直接詳細に記述することで、トラブルシューティングを容易にします。

第 1 世代の PCIe のリリース以降、効果的な PCIe テストの課題は、さまざまな種類のテスト機器とソフトウェアの継続的な開発を通じて対処されてきました。これらのツールは、パフォーマンスを正確に測定し、問題を迅速に検出し、使用条件をシミュレートして堅牢かつ包括的な分析を行うように設計されています。新しい革新的なプロトコル/ジャマーの組み合わせは、NVMe-oF などの複雑な使用条件に最適であることが実証されています。

トラフィックフローに対する高レベルの可視性と高度なトレース解析機能を備えたアナライザは、PCIe 5.0 の今後のリリースで引き続き非常に貴重なテストツールとなります。ライブトラフィックを操作する機能を備えたジャミングツールは、他の方法では不可能な強固なシミュレーションを実現します。これらの最先端の PCIe ツールの背後にあるソフトウェアは、オペレータをテストケースにシームレスに結びつける、改善し続けるインターフェイスとレポート機能の強化により、すべてを結び付け続けています。

PCI Express の当面の将来は、2019 年の 第 5 世代の PCIe のリリースによって形作られました。この改訂は、その前身と同様、 第 4 世代 の帯域幅を倍増します。性能のアップグレードに加え、第 5 世代のPCIe の物理的な違いには、短いキーとプリント基板上の改善された素材の採用が含まれます。第 5 世代は、第 3 世代および第 4 世代との下位互換性を維持しています。このため、マザーボードとアダプターカードはすぐにアップグレードする必要がありません。コンピュータハードウェアのデザイナーとメーカーは、PCIe を引き続き最新製品に組み込むため、事実上の標準という定着した位置付けが一層確立されることになります。

コンピューティングパワーとメモリーに対する増大要求は猛烈な速度で進展しています。今のところ、PCI Express バスはそのペースに沿うことができていますが、そのマージンは狭まってきています。2021 年までにリリースされる予定の PCIe 6.0 は、マシンラーニング、人工知能(AI)、およびその他の最新のアプリケーションの要求に応えるために、64 GT/s の双方向帯域幅とデータレートを驚異の 256 GB/ 秒で実現する予定です。それほど遠くない未来のデータ転送技術は、使い慣れた信頼性の高いバスと比較するとハイパーループのように思えるかもしれませんが、必然的にそうなるでしょう。スピードと帯域幅の要求を満たす上で、いかなるコンピュータ技術も重要な役割を果たすとは思えないため、PCIe 性能の継続的な進歩に対する設計者へのプレッシャーは、近い将来も続くことでしょう。

今すぐ VIAVI で PCI Expressをお試しください!

VIAVI の PCIe 製品またはソリューションで次の一歩を踏み出しませんか。

以下のフォームの 1 つに記入して、さあ始めましょう。

パンフレット

あらゆるステップでのサポート

VIAVIは、サポート、サービス、総合的なトレーニング、お客様が必要とするリソースを提供しています。これはすべて、お客様のVIAVIへの投資価値を最大化するために当社が日頃より行っていることです。

エキスパートに尋ねる

詳細、価格のお見積りについてお問い合わせください。Viaviのエキスパートがお客様のあらゆる質問にお答えします。