What is PAM4?

Learn all about the modulation technique that can be used to transmit data at high speeds.

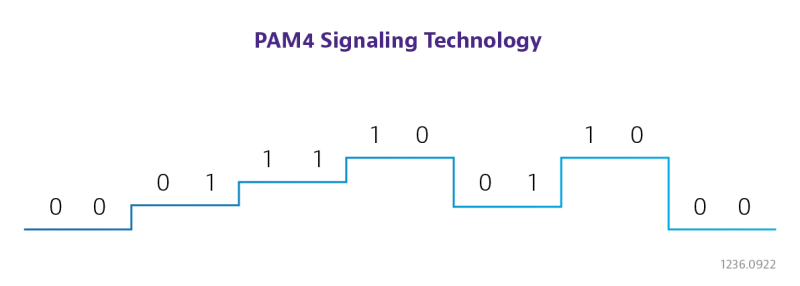

Pulse Amplitude Modulation 4-level (PAM4) supports high-speed data transmission by utilizing four amplitude levels, each containing two bits, to double the bandwidth of binary modulation methods at the same baud rate. With the symbol rate doubled by transmitting two bits instead of one, an equivalent amount of data can be transferred while operating at half the previous line rate.

The speed and spectral efficiency of PAM4 have mandated it in 802.3 .bs 400G Ethernet for both optical and electrical interfaces. Since being incorporated into the IEEE 802.3 Ethernet standard, PAM4 has also been used in other high-speed network elements including PCIe. Nearly all SERDES development today is focused on PAM4.

- PAM4 Pluggable Optical Modules or Transceivers:

Pluggable optical modules for 400Gb and 800Gb Ethernet such as QSFP-DD use PAM4 signaling on both the host electrical interface and the client optical interface. The SERDES on the host ASIC must support 100s of PAM-4 SERDES pairs which present significant signal integrity challenges. The pluggable optical module must convert these high-speed PAM4 signals to and from the optical domain to be sent over fibers. The typical reach of PAM4-encoded optical signals can be up to 10 km. Both the optical and electrical links use forward error correcting codes (FEC) to protect the link from errors, the FEC logic is carefully designed and is mandated in standards such as IEEE 802.3. - PAM4 SERDES:

SerDes technology is the basic building block used in ICs to carry high-speed data. The SERDES links serialize or deserialize data transfers between circuit board elements to optimize transmission efficiency. Parallel data streams are converted to a serial format to reduce the number of I/O interconnects. The SERDES block contains circuity to pre-distort the TX signal (pre-emphasis) as well as correct transmission effects at the receiver (equalization). Modern DSP-based SERDES used at 50G and 100G can mitigate the losses found in longer PCB traces and cables. In many cases, the user may have control over the settings to optimize the signal to minimize the bit error rate (BER). They can be very sensitive to signal impairments such as frequency and skew variation.

PAM4 vs NRZ

PAM4 is often compared to the more basic non-return-to zero (NRZ) modulation that preceded it. Both methods are currently in use, with some applications favoring the simplicity of NRZ over the speed of PAM4. Reviewing PAM4 vs NRZ signaling basic theory in more detail reveals the benefits and drawbacks of each method:

- NRZ modulation uses just two signal levels (1 or 0) to represent the digital information, with a negative voltage equating to 0 and a positive voltage representing a 1. PAM4 utilizes four discrete signal levels (0, 1, 2, 3) with each representing 2 bits of information. Since we have two bits of information sent in the same time as one bit using NRZ, PAM4 can use a reduced bandwidth channel.

- Signal to Noise Ratio (SNR) is poorer for PAM4 since the levels are more tightly spaced. This can impact the error rate on a link. The forward-error correction (FEC) technology that is often used to minimize PAM4 bit error rate (BER) is not required for all NRZ applications.

Data traffic expansion and the demand for higher bandwidth have been unrelenting. Widespread use of cloud services, 5G wireless, and the internet of things (IoT) only accelerate these trends.

- 400G and 800G Ethernet protocols have been the primary drivers of PAM4 adoption, as Ethernet speeds have outpaced the ability of conventional NRZ modulation schemes to keep up.

- PAM4 enabled the jump from 100G to 400G Ethernet by allowing for a higher data rate per lane. For example, a single 100G PAM4 transceiver can be utilized to transmit 100G over a single Ethernet lane. Early generations of 100G Ethernet required 4 electrical and optical lanes

- The current performance levels of 400G and 800G PAM4-based optics will address even the highest level of data center speed and bandwidth requirements into the foreseeable future.

- Work is underway today with 200G PAM4 SERDES ready for the needs of 1.6Tb class Ethernet.

A fiber optic link must convert electrical energy into an optical signal, transmit the optical signal over the fiber link, then convert the optical signal back into an electrical signal. Modulation is the method chosen to encode and decode information during these signal conversions.

PAM4 Modulation utilizes four different signal levels during data transmission, with each symbol representing two bits of information. At each of the four levels, the data bits are logically presented in combinations of 00, 01, 10, or 11. Gray coding is often used to manage the swing between transitions to help reduce bandwidth issues.

Power Consumption for PAM4 modulation is relatively high, due to the equalization and pre-compensation used at both ends of the line to minimize BER. This high energy utilization can also lead to power & cooling concerns, especially for 800Gb pluggable optics.

PAM4 signaling is relatively simple in principle yet challenging in execution. Developing new PAM4 testing methods, optical modules, and transceivers requires a firm grasp of important PAM4 fundamentals.

- Signal analysis: PAM4 signals are highly susceptible to noise, distortion, and dispersion. Many of the noise and jitter analysis methods developed for NRZ are still applicable, but the three-eye diagrams used to assess PAM4 signal integrity are more complex due to the interrelationships between the eyes.

- Equalization: Mitigating PAM4 signal impairment through equalization is another important facet of PAM4 technology. The methods currently in use include pre-distortion to counteract known distortion factors, and adaptive equalization to continually adjust the signal output based on received signal quality feedback.

- Physical specifications: PAM4 specifications define the form factor, voltage, wavelength, embedded clock type, and lane configuration of the module. The physical length of electrical lanes is also referred to as the reach. High PAM4 speeds can be achieved by combining multiple lanes operating at lower rates.

What is PAM4 Ethernet?

Four decades after the first IEEE standard was approved, Ethernet remains a dominant LAN and WAN technology, and one that continues to evolve. Key milestones in this progression have been linked to speed and bandwidth improvements, and PAM4 modulation has been a core part of recent standards.

The IEEE 802.3bs standard describes how eight lanes of 50 Gbps traffic with PAM4 encoding can deliver 400G Ethernet service. The adoption of this standard allowed hyperscale data centers to transition from 100G to 400G PAM4 Ethernet. 56G PAM4 SerDes configurations including various trace and cable lengths are described by the OIF-CEI-56G-PAM4 specifications.

Like the five generations that preceded it, the 6th generation of the high-speed serial expansion bus standard known as PCI Express (PCIe) doubled the speed of PCIe 5.0 while remaining fully backwards compatible. To maintain this speed doubling convention, PCIe 6.0 has incorporated PAM4 signaling.

- PAM4 Advantages: The release of the PCIe 6.0 specification in 2022 helped to address the bandwidth requirements of high-speed applications like hyperscale data centers, AI, and the IoT. The incorporation of PAM4 makes PCIe data rates of 64 GT/sec possible while reducing the channel loss and crosstalk.

- PAM4 Efficiency: To compensate for increased link sensitivity with PAM4, forward error correction was added to the Gen6 standard. The potential loss of efficiency from FEC was offset by the reduced overhead from fixed packet sizes.

- Interoperability: Although PCIe 6.0 uses PAM4 signaling instead of the NRZ signaling used in previous PCIe generations, it is completely backwards compatible.

PAM4 Testing

The four-level modulation of PAM4 unlocks additional speed and bandwidth, but also leads to additional complexity and challenges for PAM4 testing.

- Error classification: Even under optimal conditions, PAM4 modulation induces some level of errors, so simple error counting test methods no longer suffice. Instead, the test method must identify whether the errors were produced during a symbol transition, isolated to a specific burst, or induced by external interference. Errors need to be carefully fingerprinted and characterized. In many cases live traffic is required to get true ‘FEC’ performance.

- PAM4 SerDes Testing: SerDes testing must also distinguish issues related to the high-speed link from those that originated elsewhere in the circuit.

- PAM4 Module Testing: Test platforms for PAM4 transceiver modules must be capable of delivering the requisite SERDES speed, power, and cooling needed to verify high-speed signaling and FEC performance. The VIAVI ONT-800 builds on the success of past generations of multi-protocol, multi-port test platforms for R&D and production to provide a deeper level of insight during PAM4 and SerDes testing.